# *Ultralow-Voltage Bilayer Graphene Tunnel FET*

### **Gianluca** Fiori

Dipartimento di Ingegneria dell'Informazione: Elettronica, Informatica, Telecomunicazioni, Università di Pisa

### **Giuseppe Iannaccone**

Dipartimento di Ingegneria dell'Informazione: Elettronica, Informatica, Telecomunicazioni, Università di Pisa

G. Fiori, G. Iannaccone, *Ultralow-Voltage Bilayer Graphene Tunnel FET*, IEEE Electron Device Letters, **30**, 10, pp.1096-1098 (2009)

## Ultralow-Voltage Bilayer Graphene Tunnel FET

Gianluca Fiori and Giuseppe Iannaccone

Abstract—In this letter, we propose the bilayer graphene tunnel field-effect transistor (TFET) as a device suitable for fabrication and circuit integration with present-day technology. It provides high  $I_{\rm on}/I_{\rm off}$  ratio at ultralow supply voltage, without the limitations in terms of prohibitive lithography and patterning requirements for circuit integration of graphene nanoribbons. Our investigation is based on the solution of the coupled Poisson and Schrödinger equations in three dimensions, within the nonequilibrium Green's function formalism on a Tight Binding Hamiltonian. We show that the small achievable gap of only few hundreds of millielectronvolts is still enough for promising TFET operation, providing a large  $I_{\rm on}/I_{\rm off}$  ratio in excess of  $10^3$  even for a supply voltage of only 0.1 V. A key to this performance is the low quantum capacitance of bilayer graphene, which permits to obtain an extremely small subthreshold swing S smaller than 20 mV/dec at room temperature.

*Index Terms*—Bilayer graphene, low-power device, non-equilibrium Green's function (NEGF), tunnel field-effect transistor (TFET).

#### I. INTRODUCTION

**W** [1]–[4] have shown the possibility of inducing an energy gap ( $E_{gap}$ ) in bilayer graphene by means of an applied electric field perpendicular to the graphene plane. This property could open the possibility of fabricating carbon-based electron devices, for which a semiconducting gap is required, with state-of-the-art lithography. Let us stress that the alternative option of inducing a gap by means of lateral confinement to fabricate graphene nanoribbon field-effect transistors (FETs) [5] requires single-atom control and prohibitive lithography to define widths close to 1 nm [6].

Since the largest attainable  $E_{\text{gap}}$  in bilayer graphene is of few hundreds of millielectronvolts, band-to-band tunneling strongly limits device performance, so that the  $I_{\text{on}}/I_{\text{off}}$  ratio of the drain current is typically smaller than 10 [7].

One can, however, turn this limitation into an advantage, fully exploiting band-to-band tunneling instead of avoiding it, like in tunnel FETs (TFETs), which have been widely

Manuscript received June 5, 2009; revised July 7, 2009. First published September 9, 2009; current version published September 29, 2009. This work was supported in part by the EC Seventh Framework Program under Project GRAND (Contract 215752), by the Network of Excellence NANOSIL (Contract 216171), and by the European Science Foundation EUROCORES Program Fundamentals of Nanoelectronics, through fundings from the CNR and the EC Sixth Framework Program under Project DEWINT (Contract ERAS-CT-2003-980409). The review of this letter was arranged by Editor X. Zhou.

The authors are with the Dipartimento di Ingegneria dell'Informazione: Elettronica, Informatica, Telecomunicazioni, Università di Pisa, 56126 Pisa, Italy (e-mail: gfiori@mercurio.iet.unipi.it; g.iannaccone@iet.unipi.it).

Color versions of one or more of the figures in this letter are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/LED.2009.2028248

investigated in the past through experiments and simulations, considering different channel materials [8]–[10].

The main appeal of TFETs is the possibility of obtaining a subthreshold swing S well below that obtained in conventional FETs, which would in turn allow one to strongly reduce the supply voltage for digital logic well below 0.5 V, and consequently the power consumption [8].

In this regard, it has been recently observed [11] that 1-D carbon-based devices are more promising than planar silicon devices, because of the small carrier effective mass that enhances the  $I_{\rm on}$  current, and of the small quantum capacitance in the ON-state, which guarantees good electrostatic control of the channel through the gate voltage, improving S.

In this letter, we propose the realization of an ultralowpower bilayer graphene TFET (BG-TFET) and investigate its performance by means of numerical simulations based on the self-consistent solution of the 3-D Poisson and Schrödinger equations, within the nonequilibrium Green's function (NEGF), implemented in our open source code NanoTCAD ViDES [12].

We show that a large  $I_{\rm on}/I_{\rm off}$  ratio in excess of  $10^3$  can be obtained for a voltage  $V_{\rm DD}$  of only 0.1 V. The low quantum capacitance of bilayer graphene allows us to grab the advantages provided by 1-D carbon channels also with a planar—more easily manufacturable—structure, and to achieve very low S.

#### **II. RESULTS AND DISCUSSION**

The Schrödinger equation has been solved within a  $p_z$  orbital basis set in the real space. Implementation details can be found in [7] and [13].

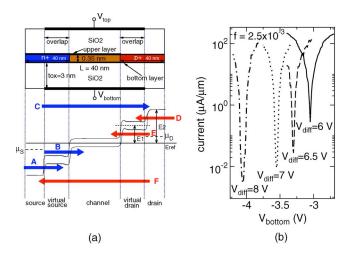

The device structure is shown in Fig. 1(a). The considered device is a double-gate BG-TFET, driven by two independent gates, biased with voltages  $V_{\text{top}}$  and  $V_{\text{bottom}}$ . The channel length L is 40 nm, and the p<sup>+</sup> and n<sup>+</sup> reservoirs are 40 nm long and doped with molar fraction f. The bilayer graphene is embedded in a 3-nm-thick SiO<sub>2</sub> insulator with relative dielectric constant  $\varepsilon_r = 3.9$ . A gate overlap has also been taken into account, whose effects will be discussed later on.

In Fig. 1(a), a band edge profile of the TFET in the OFF-state is also shown. Since the potential in the vertical direction falls linearly, the device is in the OFF-state (minimum current in the channel) for  $V_{\text{bottom}} = V_{\text{min}} \equiv (V_{\text{top}} - V_{\text{bottom}})/2 + V_{\text{DS}}/2$ , where  $V_{\text{DS}}$  is the drain-to-source voltage.

The conduction and valence bands can be divided in five subregions along the transport direction: the source, the socalled virtual source, the channel, the virtual drain, and the drain. Deep in the source and drain regions, the conduction and the valence bands coincide because the vertical electric field rapidly goes to zero. A gap is induced in all the regions

0741-3106/\$26.00 © 2009 IEEE

Fig. 1. (a) Sketch of the double-gate bilayer graphene TFET: the channel length is 40 nm, and n<sup>+</sup> and p<sup>+</sup> reservoirs are 40 nm long with molar fraction f. The device is embedded in a 3-nm-thick SiO<sub>2</sub> dielectric.  $V_{\rm top}$  and  $V_{\rm bottom}$  are the voltages applied the top and bottom gate, respectively. Gate overlap has been also considered. Below, band edge profile of the device in the OFF-state. (b) Transfer characteristics of the double-gate BG-TFET for different  $V_{\rm diff}$ . f is equal to  $2.5 \times 10^{-3}$  and  $V_{\rm DS} = 0.1$  V.

surrounded by the top and the bottom gates, where a differential voltage  $V_{\text{diff}} \equiv V_{\text{top}} - V_{\text{bottom}}$  is imposed, i.e., in the virtual source and drain regions and in the channel.

Six different fluxes of carriers contribute to transport, identified with a letter in Fig. 1(a): tunneling electrons (A and B fluxes), tunneling holes (E and D fluxes), and thermally emitted electrons (C) and holes (F). In order to obtain a small  $I_{\rm off}$ , all mentioned fluxes have to be minimized through proper band engineering.

One solution could be inducing a large energy gap, which translates in imposing a large vertical electric field. This option is, however, limited by the breakdown field of the oxide, and by the gate leakage current. To this purpose, we have chosen  $SiO_2$  as a gate dielectric, which guarantees an intrinsic breakdown field close to 14 MV/cm [14] (well above the simulated vertical electric fields), and a large graphene/SiO<sub>2</sub> band offset (larger than 3 eV), which ensures very small gate leakage currents.

The molar fraction of the source and drain leads instead determines  $E_1$  and  $E_2$ , the difference between the midgap potential in the channel ( $E_{ref}$ ) and the midgap in the virtual drain and in the drain, respectively (same considerations obviously follow for the source): the higher f, the higher  $E_1$  and  $E_2$ . Decreasing  $E_1$  and  $E_2$  can help in reducing E and D (or A and B in the source), but in turns increases of thermionic emission (C and F).

Let us focus on the performance of the BG-TFET with ultralow supply voltage  $V_{\rm DD} = 0.1$  V. In Fig. 1(b), we show the transfer characteristics as a function of  $V_{\rm bottom}$  of a device with molar fraction  $f = 2.5 \times 10^{-3}$ , for fixed differential gate voltages  $V_{\rm diff} = 6, 6.5, 7, \text{ and } 8$  V.

As can be noted, differently from what happens in doublegate BG-FETs [7], the BG-TFET can be perfectly switched off, with a steep subthreshold behavior (always smaller than 20 mV/dec) and a large  $I_{\rm on}/I_{\rm off}$  ratio also for a very low  $V_{\rm DD}$ (e.g.,  $I_{\rm on}/I_{\rm off} = 4888$  for  $V_{\rm diff} = 8$  V).

$\begin{array}{c} \text{TABLE I}\\ I_{\mathrm{off}} \text{ Ratios, } E_{\mathrm{gap}} \text{ Computed in the Middle of the Channel $\mathcal{E}$,}\\ \text{ the Electric Field in the Middle of the Channel, and}\\ \text{ Subthreshold Swing $S$ for Different $V_{\mathrm{diff}}$} \end{array}$

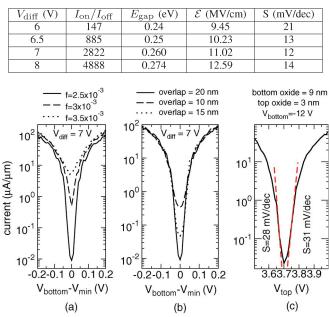

Fig. 2. (a) Transfer characteristics of BG-TFETs for  $V_{\rm diff} = 7$  V,  $V_{\rm DS} = 0.1$  V, and different molar fractions f.  $V_{\rm min} = -3.55$  V. (b) Transfer characteristics of BG-TFET for  $V_{\rm diff} = 7$  V,  $V_{\rm DS} = 0.1$  V, and different gate overlap.  $V_{\rm min} = -3.55$  V. (c) Transfer characteristic for a device with asymmetric oxide thicknesses: The top oxide thickness is 3 nm, and the bottom oxide thickness is 9 nm.  $V_{\rm bottom}$  is fixed to -12 V and  $V_{\rm DS} = 0.1$  V.

The capability of electrostatically tuning the energy gap can be fully exploited in BG-TFET, as shown in Table I, where  $I_{\rm on}/I_{\rm off}$  increases by a factor of 33, varying  $V_{\rm diff}$  from 6 to 8 V, as also experimentally demonstrated in [15].

Due to the large vertical electric field, particular attention has also to be posed on the gate leakage current. We can estimate its value using a well-tested analytical model for Si–SiO<sub>2</sub> gate stacks based on WKB approximation of the triangular barrier [16]. We find that 3-nm gate oxide is sufficient to obtain a gate current of the order of  $10^{-6} \ \mu A/\mu m$  for  $V_{\text{diff}} = 7 \text{ V}$ , and  $10^{-4} \ \mu A/\mu m$  for  $V_{\text{diff}} = 8 \text{ V}$ , i.e., negligible with respect to the smallest drain currents considered in our simulations.

In Fig. 2(a), we show the transfer characteristics as a function of  $V_{\text{bottom}}$ , for  $V_{\text{diff}} = 7$  V, and for different dopant molar fractions f in the drain and source leads. As f is increased, the  $I_{\text{on}}/I_{\text{off}}$  ratio degrades, since  $I_{\text{off}}$  increases, while  $I_{\text{on}}$  remains almost constant.

In Fig. 2(b), we show the transfer characteristics as a function of gate overlap. As shown, the smaller the overlap, the higher the  $I_{\text{off}}$  current, since it is the energy gap of the virtual reservoirs that suppresses tunneling from contacts to the channel.

In order to investigate the performance of single-gate devices, we have also performed simulations of a device with asymmetric gate oxide thicknesses [Fig. 2(c)]: the top oxide is 3 nm, and the bottom oxide is 9 nm. In this case, the bottom gate voltage is kept at a constant bias of -12 V, whereas the top gate is used as the control gate. This solution, with a common back gate at constant voltage for all FETs, is obviously more suitable for circuit integration.

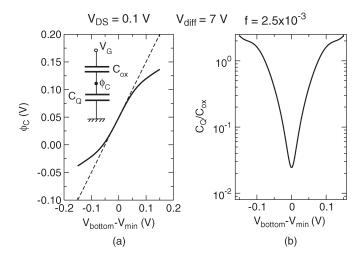

Fig. 3. (a) (Solid line) Electrostatic potential in the middle of the channel  $\phi_C$  as a function of the bottom gate voltage. The dashed line refers the case in which the gate control is ideal, i.e.,  $\phi_c = (V_{\text{bottom}} - V_{\min}) + V_{\text{DS}}/2$ . In the inset, the equivalent capacitance circuit of the device is shown. (b) Ratio of the quantum capacitance  $C_Q$  and the oxide capacitance  $C_{\text{ox}}$ .

As can be noted, an  $I_{\rm on}/I_{\rm off}$  ratio of few hundreds can be still obtained. The subthreshold swing (and then the  $I_{\rm on}/I_{\rm off}$  ratio) can be improved with a thicker bottom oxide of the order of 100 nm, which would reduce the capacitive coupling between channel and bottom gate. We, however, limited our analysis to 9 nm, because of numerical convergence problems encountered when dealing with larger structures.

As noted in [11], 1-D channels are typically more appealing for tunneling device applications than planar 2-D channels, since their quantum capacitance  $C_Q$  is smaller than the electrostatic capacitance  $C_{\rm ox}$  even in the ON-state. Such condition guarantees a good gate control over the potential barrier and larger  $I_{\rm on}/I_{\rm off}$ .

In Fig. 3(a), we show  $\phi_C$ , the electrostatic potential in the middle of the channel, as a function of the bottom gate voltage, for  $f = 2.5 \times 10^{-3}$  and  $V_{\text{diff}} = 7$  V. On the same plot, we also show the line  $\phi_C = V_{\text{bottom}} - V_{\text{min}} + V_{\text{DS}}/2$ , corresponding to ideal control of the channel potential from the gate voltage. As shown, also for larger gate voltages,  $\phi_C$  reasonably follows  $V_{\text{bottom}}$ , and no channel potential saturation is observed. As indeed shown in Fig. 3(b), where the ratio  $C_Q/C_{\text{ox}}$  is depicted, for small voltages the device is working in the Quantum Capacitance Limit (i.e.,  $C_Q \ll C_{\text{ox}}$ ), whereas for larger values  $C_Q$  is comparable with  $C_{\text{ox}}$ . However, it never reaches the condition  $C_Q \gg C_{\text{ox}}$  as in silicon TFETs. As a consequence, despite its bidimensionality, bilayer graphene is appealing for tunneling devices applications.

#### **III.** CONCLUSION

In conclusion, we have performed a numerical analysis of a BG-TFETs, based on the self-consistent solution of the 3-D Poisson/Schrödinger equations, within the NEGF formalism. Large  $I_{\rm on}/I_{\rm off}$  ratios can be obtained even for an ultralow supply voltage of only 100 mV, thanks to an extremely steep subthreshold slope. The low quantum capacitance of bilayer graphene allows the BG-TFET to have most of the advantages of 1-D TFETs, but none of the disadvantages in terms of structure patterning and lithography. Indeed, since presentday lithography is adequate for the fabrication of BG-TFETs, and the single-gate driving option with constant bottom gate bias is suitable for planar integration, we consider the device very promising for fabrication experiments and circuit integration.

#### REFERENCES

- E. McCann and V. I. Falko, "Landau-level degeneracy and quantum hall effect in a graphite bilayer," *Phys. Rev. Lett.*, vol. 96, no. 8, p. 086 805, Mar. 2006.

- [2] J. Nilsson, A. H. Castro Neto, F. Guinea, and N. M. R. Peres, "Electronic properties of graphene multilayers," *Phys. Rev. Lett.*, vol. 97, no. 26, p. 266 801, Dec. 2006.

- [3] E. V. Castro, K. S. Novoselov, V. Morozov, N. M. R. Peres, J. M. B. Lopes dos Santos, J. Nilsson, F. Guinea, A. K. Geim, and A. H. Castro Neto, "Biased bilayer graphene: Semiconductor with a gap tunable by the electric field effect," *Phys. Rev. Lett.*, vol. 99, no. 21, p. 216 802, Nov. 2007.

- [4] V. Ryzhii, M. Ryzhii, A. Satou, T. Otsuji, and N. Kirova, "Device model for graphene bilayer field-effect transistor," *J. Appl. Phys.*, vol. 105, p. 104 510, 2009.

- [5] Z. Chen, Y.-M. Lin, M. J. Rooks, and P. Avouris, "Graphene nano-ribbon electronics," *Phys. E*, vol. 40, no. 2, pp. 228–232, Dec. 2007.

- [6] G. Fiori and G. Iannaccone, "Simulation of graphene nanoribbon fieldeffect transistors," *IEEE Electron Device Lett.*, vol. 28, no. 8, pp. 760–762, Aug. 2007.

- [7] G. Fiori and G. Iannaccone, "On the possibility of tunable-gap bilayer graphene," *IEEE Electron Device Lett.*, vol. 30, no. 3, pp. 261–264, Mar. 2009.

- [8] W. Hansch, C. Fink, K. Schulze, and I. Eisele, "A vertical MOS-gated Esaki tunneling transistor in silicon," *Thin Solid Films*, vol. 369, no. 1, pp. 387–389, Jul. 2000.

- [9] S. O. Koswatta, M. S. Lundstrom, and D. E. Nikonov, "Influence of phonon scattering on the performance of p-i-n band-to-band tunneling transistors," *Appl. Phys. Lett.*, vol. 92, no. 4, p. 043 125, Jan. 2008.

- [10] P. Zhao, J. Chauhan, and J. Guo, "Computational study of tunneling transistor based on graphene nanoribbon," *Nano Lett.*, vol. 9, no. 2, pp. 684– 688, Feb. 2009.

- [11] J. Knoch and J. Appenzeller, "Tunneling phenomena in carbon nanotubes field-effect transistors," *Phys. Stat. Sol.*, vol. 205, no. 4, pp. 679–694, 2008.

- [12] [Online]. Available: http://www.nanohub.org/tools/vides

- [13] G. Fiori and G. Iannaccone, "Performance analysis of graphene bilayer transistors through tight-binding simulations," in *Proc. 13th Int. Workshop Comput. Electron.*, Beijing, China, May 27–29, 2009, pp. 1–4.

- [14] A. Campera, G. Iannaccone, and F. Crupi, "Modeling of tunnelling currents in Hf-based gate stacks as a function of temperature and extraction of material parameters," *IEEE Trans. Electron Devices*, vol. 54, no. 1, pp. 83–89, Jan. 2007.

- [15] Y. Zhang, T. Tang, C. Girit, Z. Hao, M. C. Martin, A. Zettl, M. Crommie, Y. Shen, and F. Wang, "Direct observation of a widely tunable bandgap in bilayer graphene," *Nature*, vol. 459, no. 7248, pp. 820– 823, Jun. 2009.

- [16] M. Depas, B. Vermeire, P. W. Mertens, R. L. Van Meirhaeghe, and M. M. Heyns, "Determination of tunnelling parameters in ultra-thin oxide layer poly–Si/SiO<sub>2</sub>/Si structure," *Solid State Electron.*, vol. 38, no. 8, pp. 1465–1471, Aug. 1995.