# Extraction of the trap distribution responsible for SILCs in MOS structures from measurements and simulations of DC and noise properties

# A. Nannipieri

ISE Integrated Systems Engineering AG, Zurich

## **Giuseppe Iannaccone**

Dipartimento di Ingegneria dell'Informazione: Elettronica, Informatica, Telecomunicazioni, Università di Pisa

# **Felice Crupi**

Dipartimento di Elettronica, Informatica e Sistemistica, Università della Calabria

A. Nannipieri, G. Iannaccone, F. Crupi, *Extraction of the trap distribution responsible for SILCs in MOS structures from measurements and simulations of DC and noise properties*, Microelectronics Reliability, **44**, pp.1497-1501 (2004).

Microelectronics Reliability 44 (2004) 1497-1501

### MICROELECTRONICS RELIABILITY

www.elsevier.com/locate/microrel

# Extraction of the trap distribution responsible for SILCs in MOS structures from measurements and simulations of DC and noise properties

A.Nannipieri<sup>a,b</sup>, G. Iannaccone<sup>b</sup>, F. Crupi<sup>c</sup>

"ISE Integrated Systems Engineering AG, Affolternstrasse 52, CH-8050 Zurich, Switzerland Dipartimento di Ingegneria dell'Informazione: Elettronica, Informatica, Telecomunicazioni, Universita' degli Studi di Pisa and IEIIT-CNR, Via Caruso, I-56122 Pisa, Italy Dipartimento di Elettronica, Informatica e Sistemistica, University of Calabria, Italy

### **Abstract**

In this paper we present a detailed investigation of the properties of SILCs through MOS capacitors, focusing our attention on the extraction of the trap distribution from DC and shot noise properties of the structure. Our model of SILCs, based on inelastic Trap-Assisted Tunneling, is able to reproduce both the J-V characteristics and the shot noise suppression, explaining the latter in terms of Pauli Exclusion Principle and Coulomb repulsion. Fitting of numerical results with J-V characteristics before and after stress led to the extraction of distributions of native traps and stress-induced traps, respectively. In order to extract a unique trap distribution, comparison with shot noise measurements revealed to be mandatory. The combined effect of the two types of traps explains the DC and noise properties for the range of oxide thickness comprised between 4 nm and 10 nm, in which SILCs play a dominant role. © 2004 Published by Elsevier Ltd.

### 1. Introduction

Recent studies [1]-[4] agree in identifying Trap-Assisted Tunneling (TAT) as the physical mechanism responsible for Stress-Induced Leakage Currents (SILCs) through thin SiO<sub>2</sub> MOS capacitors: high electric fields, applied to MOS structures, generate traps in the oxide which introduce localized energy levels in the oxide gap. On the contrary, the issue is still controversial as far as trap properties are concerned: both the energy distribution of traps and their microscopic nature are a matter of discussion.

The good fitting between numerical results and experimental data, as far as DC current-voltage characteristics are concerned, is not sufficient to

determine the trap distribution in a unique way: for this reason, an investigation of other features of SILCs is needed. For example, the study of SILC transient components leads to the result that SILC DC component is due to traps located in correspondence with the silicon electrode gap [2].

Our results have been reached with the following consideration: Pauli exclusion principle and Coulomb repulsion prevent two electrons from occupying the same trap, therefore introducing correlation in the motion of carriers. This causes the suppression of the power spectral density of shot noise, related to SILC current, with respect to the full value S = 2qI, obtained for current through fresh oxides, and typical of uncorrelated motion of electrons.

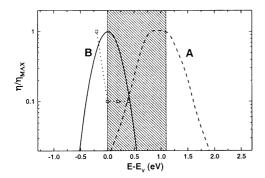

Fig. 1. Comparison between normalized trap distributions obtained with our model (thick solid line) and those described in [1] (A, dotted line) and in [2] (B, symbols). The patterned region corresponds to silicon energy gap. Energies on the abscissa axis are related to the top of the silicon valence band.

We used our model of TAT to extract an energy distribution of traps, in the oxide gap, able to represent both J-V curves and shot noise suppression: numerical results are compared to experimental data for two sample capacitors, with oxide thickness of 6 nm and 10 nm respectively, already presented in Ref. [4]. We extracted a Gaussian distribution  $\eta(E)$  of SILC traps, as a function of the trap energy E in the oxide gap, and a uniform distribution for native traps, i.e. those present also in fresh oxides: the combined effect of the two distributions provides good fitting with experiments if the oxide thickness  $t_{ox}$  is in the range 4 nm-10 nm. Experimental results and theoretical studies show that SILC is negligible for  $t_{ox} > 10$  nm whereas for  $t_{ox} < 3$ nm current due to bulk traps is about two orders of magnitude lower than the current due to interface traps [5]-[7].

### 2. Model and experimental results

The proposed model is described in detail in Ref. [4]. The definition of the capture cross section has been generalized as it contains not only spatial but also energetic information, through a half-width energy parameter  $\Gamma$ : the capture cross section is inversely proportional to  $(E_t - E)^2 + \Gamma^2$ , where  $E(E_t)$  is the electron (trap) energy. The parameter  $\Gamma$  is therefore strictly connected with the inelasticity of the transport mechanism and in our simulations has been varied in the range 0.1 meV-10 meV.

From the capture section we can determine

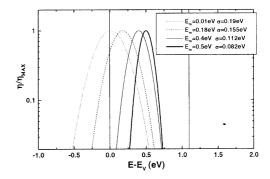

Fig. 2. Extracted trap gaussian distributions providing good fit with J-V curves: corresponding mean values and standard deviations are shown in the inset. The region between the two vertical lines corresponds to silicon energy gap.

generation and recombination rates and, as a consequence, the current I' and its associated power spectral density S' related to a single trap: integrating these quantities over  $E_a$ , in the oxide energy gap, and over x', in the oxide thickness and assuming  $\eta$  as the trap density per unit volume per unit energy, the total current density  $J_{TAT}$ , the total noise spectral density  $S_{TAT}$  and the Fano factor  $\gamma_{TAT}$  can be obtained:

$$J_{SHC} = \iint I' \eta \left( E_{\alpha}, x' \right) dE_{\alpha} dx' \tag{1}$$

$$S_{SILC} = \iint S' \eta \left( E_{\alpha}, x' \right) dE_{\alpha} dx' \tag{2}$$

$$\gamma_{SILC} = \frac{S_{SILC}}{2qJ_{SILC}} = \frac{\iint S'\eta(E_{\alpha}, x')dE_{\alpha}dx'}{\iint I'\eta(E_{\alpha}, x')dE_{\alpha}dx'}$$

(3)

The SILC Fano factor  $\gamma_{SILC}$ , i.e. the shot noise suppression due to stress-generated traps, in the current range where SILC is predominant, is about 0.75 for the 10 nm oxide and between 0.63 and 0.83 for the 6 nm oxide.

### 3. Numerical results

### 3.16 nm oxide

Numerical simulations for fresh oxides fit reasonably the experimental characteristics in the FN region whereas the computed current is about an order of magnitude lower than the measured one for low gate

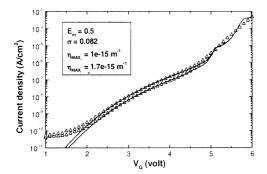

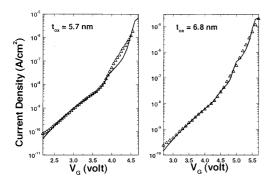

Fig. 3. Comparison between experimental data (symbols) and numerical results (solid lines) for two different duration stress times. Parameters of trap distribution used in the simulation are shown in the inset.

voltages. As a consequence, we assumed the presence of traps, the so-called native traps, even in fresh oxides. Simulations, with native traps assumed to be uniformly distributed, in energy and in space, between 1.5 eV and 2.5 eV above the bottom of the oxide conduction band give satisfactory results. In this case electrons involved in the transitions are those of the cathode conduction band.

On the contrary, for the oxide after stress, a nonuniform distribution of traps in the oxide can be extracted referring to equation (1): the left-hand side can be determined by subtracting the fresh current component, i.e. current not assisted by traps, from the total current and the elementary contribute I' in the right-hand side can be numerically obtained using our simulation code. Equation (1) is therefore an integral equation with  $\eta$  as the unknown. We assume  $\eta$  to be independent of x', according to [1], transforming the integral equation into a linear algebraic system: its solution is a distribution that we interpolate with the Gaussian curve shown, in thick solid line, in Fig. 1. Therefore the trap distribution can be expressed as a function of three parameters only:  $E_m$ ,  $\sigma$  and  $\eta_{MAX}$ , the Gaussian maximum value.

In the same figure our distribution is compared to others (all the distributions are normalized to their maximum value) obtained using models described in [1] and [2] respectively: all the three models agree in locating traps inside, or at least very close to, the silicon energy gap and, as a consequence, consider SILC current due to transitions involving electrons of the cathode valence band. This result is compatible with quantum yield measurements according to which the energy of electrons contributing to SILCs is 1.5 eV

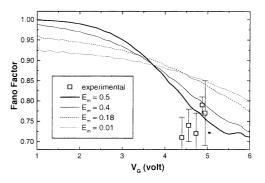

Fig. 4. Shot noise suppression for the 6nm-thick oxide, as a function of the applied gate voltage. Symbols + error bars represent measurements on different 6-nm thick oxide sample MOS capacitors.

lower than that of FN tunneling electrons [3].

Further simulations were performed trying to obtain the mean value  $E_m$  and the standard deviation  $\sigma$  that provide the best fit for the J-V curves in the least square sense. It is possible to obtain a good fit for different values of  $E_m$  in the range between 4.8 eV and 5.3 eV above the oxide valence band. In Fig. 2 distributions used in the above simulations are shown together with their corresponding  $E_m$  and  $\sigma$  values.

In Fig. 3 a typical result, obtained with the distribution with  $E_m = 0.5 \text{ eV}$ , is shown (numerical and experimental data differ for less than 1% in the whole range for the gate voltage in which SILC is predominant): for small anode voltages the good fitting between numerical and experimental curves goes off mainly because of the instrumentation sensitivity and, possibly, an additional contribution from interface traps not considered in our model [5], [6]. The application of the same stress voltage for different periods of time causes a translation of the curve whereas its shape remains the same: associated values for  $\eta_{MAX}$  are shown in the inset.

The fact that different values for  $E_m$  and  $\sigma$  allow to obtain a perfect fitting of J-V curves confirm that DC properties are not sufficient to univocally determine the trap density of states. For this reason, we obtain further information from the shot noise. Fig. 4 shows numerical results for Fano factor of the SILC component,  $\gamma_{SILC} = S_{SILC} / 2qI_{SILC}$  where  $S_{SILC}$  is the power spectral density of the SILC component, and  $I_{SILC}$  is the SILC current. Curves have been obtained using the trap distributions of Fig. 2 with the same pattern. It is evident that the closer is  $E_m$  to the middle of the silicon oxide gap, the lower  $\gamma_{SILC}$ . Error bars

Fig. 5. Comparison between experimental data (symbols) extracted from [1] and numerical results (solid line) obtained with our simulation

represent the dispersion of measurements, performed on different samples. Referring to the thick solid curve, for very low voltages  $\gamma_{SILC}$  is close to unity because SILC is negligible and the current is stuck at the noise measurement system level. As the assisted current increase,  $\gamma_{SILC}$  goes down.

The relation between  $\gamma_{TOT}$  and  $\gamma_{SILC}$  is [4]:

$$\gamma_{TOT} = 1 - \left(1 - \gamma_{SH,C}\right) \cdot \frac{I_{SH,C}}{I_{TOT}} \tag{4}$$

therefore  $\gamma_{TOT}$  tends to one as  $I_{SILC}$  becomes negligible with respect to not-assisted current for high voltages, but this does not apply to  $\gamma_{SILC}$ .

In order to test the validity of our distribution for a large interval of oxide thickness, we extracted experimental data from [1]. We made the assumption that current for high gate voltages is due only to Fowler-Nordheim tunneling and fitting in that region has been used to determine the proper oxide thickness to be used in our code. We used  $m_{e,ox} = 0.6m_0$  as the electron effective mass in the oxide conduction band. The good agreement between experimental data and simulation results, evident from fig. 5, is the confirmation that our model can be successfully used to describe all the main features of SILC for oxide thickness in the range 4-7 nm, i.e. the same as [1].

### 3.2 10 nm oxide

10 nm can be considered as the limit above which SILC is completely negligible with respect to unassisted current. Referring to [4, fig. 2] and [4, fig. 6], in which experimental data for the two samples are

shown, the different qualitative behavior is apparent: for the 6 nm oxide, and for the samples extracted from [1], the curves exhibit a decreasing slope at low fields in the semilogarithmic scale, whereas the slope is increasing for the thicker oxide. The fact that the notassisted contribution, in the latter case, is reduced is confirmed by the fact that J-V curves before and after stress are very similar and do not show the change of slope typical of thinner oxides. We deduced that a different behavior should be due to traps of different nature and, according to this reasoning, simulation showed that native traps play a very important role. Even if the use of a uniform distribution is providing qualitatively good results, we are currently testing a method for the extraction of the actual native trap distribution.

In terms of electric field in the oxide instead of the gate voltage, SILCs are predominant in the same range between 5 MV/cm and 7 MV/cm for both the two samples [8]: with increasing electric fields, native traps starts dominating for the thicker oxide whereas, for the thinner one, their contribution is negligible with respect to that of not-assisted tunneling.

### 4. Conclusion

In this paper the results of a study on the tunneling currents through oxides before and after electric field stress was shown. A one-dimensional self-consistent Poisson-Schrödinger solver was used for computing the (direct) not assisted current, modeling the trap-assisted tunneling current at low electric fields and extracting traps' distributions in the oxide. Whereas for thin oxides J-V curves and Fano factor suppression can be fully described in terms of SILCs traps, for thicker oxides the effect of native traps is important: their location was identified in correspondence of the silicon conduction band even if their exact distribution is still under investigation. A Gaussian distribution located in correspondence of the silicon energy gap was extracted for the SILC traps, instead, in good agreement with other previous works in literature. The different J-V characteristic profiles between thin and thick oxide regimes is explained in terms of contribution of traps of different nature, involving electrons tunneling from VB and CB respectively. The good fitting with experimental data for the shot noise suppression is a further confirmation for the validity of our results as well as a mandatory condition for the identification of a unique trap distribution.

### Acknowledgements

Support is gratefully acknowledged from the EU through the SINANO Network of Excellence (EU Contract 506844), from the Italian MIUR through the FIRB Project "Sistemi miniaturizzati per elettronica e fotonica", and from the Fondazione Cassa di Risparmio di Pisa.

### References

- [1] B. Riccò, G. Gozzi, M. Lanzoni, "Modeling and Simulation of Stress-Induced Leakage Current in Ultrathin SiO<sub>2</sub> Films", IEEE Trans. Electron Devices, vol. 45, No. 7, pp. 1554-1560, 1998.

- [2] D. Ielmini A.S. Spinelli, M.A. Rigamonti, A. Lacaita, "Modeling of SILC Based on Electron and Hole Tunneling", IEEE Trans. Electron Devices, vol. 47, No. 6, pp. 1258-1272, 2000

- [3] S. Takagi, N. Yasuda, A. Toriumi, "Experimental Evidence of Inelastic Tunneling in Stress- Induced Leakage Current", IEEE Trans. Electron Devices, vol. 46, No. 2, pp. 335-341, 1999; "A new I-V model for stress-induced leakage current including inelastic tunneling", IEEE Trans. Electron Devices, vol. 45, No. 6, pp. 348-354, 1999.

- [4] G. Iannaccone, F. Crupi, B. Neri, S. Lombardo, "Theory and experiment of suppressed shot noise in Stress-Induced-Leakage-Currents", IEEE Trans. Electron Devices, vol. 50, No. 5, pp. 1363-1369, 2003.

- [5] A. Ghetti, "Tunneling into Interface States as a Reliability Monitor for Ultrathin Oxides", IEEE Trans. Electron Devices, vol. 47, No. 12, pp. 2358-2365, 2000.

- [6] F. Crupi, C. Ciofi, A. Germano', G. Iannaccone, J. H. Stathis, S. Lombardo, "On the role of interface states in low-voltage leakage currents of metal-oxide semiconductor structures", Applied Physics Letters, vol. 80, no. 24, 2002.

- [7] R. Moazzami, C. Hu, "Stress-Induced Current in Thin Silicon Dioxide Films", IEDM tech. Dig. pp. 139-142, 1992

- [8] M. Kimura, H. Koyama, "Stress-Induced Low Level Leakage Mechanism in Ultrathin Silicon Dioxide Films Caused by Neutral Oxide Trap Generation", Reliability Physics Symposium, pp. 167-172, 1994