# Comparison of advanced transport models for nanoscale MOSFETs

## **P.Palestri**

DIEGM, University of Udine

### **C. Alexander**

University of Glasgow

**A. Asenov** University of Glasgow

**G. Baccarani**

ARCES, University of Bologna

**A. Bournel** IEF, University Paris–Sud

## M. Braccioli

ARCES, University of Bologna

## B. Cheng

University of Glasgow

## P. Dollfus

IEF, University Paris-Sud

A. Esposito

ETH Zürich

**D. Esseni** DIEGM, University of Udine

A. Ghetti

Numonyx, R&D – Technology Development - Agrate Brianza

## C. Fiegna

P. Palestri, C. Alexander, A. Asenov, G. Baccarani, A. Bournel, M. Braccioli, B. Cheng, P. Dollfus, A. Esposito, D. Esseni, A. Ghetti, C. Fiegna, G. Fiori, V. Aubry-Fortuna, G. Iannaccone, A. Martinez, Majkusiak B., S. Monfray, S. Reggiani, C. Riddet, J. Saint-Martin, E. Sangiorgi, A. Schenk, L. Selmi, L. Silvestri, J. Walczak, *Comparison of advanced transport models for nanoscale MOSFETs*, 10th International Conference on Ultimate Integration of Silicon, pp.125-128, Aachen 2009.

# Università di Pisa

ARCES, University of Bologna

## **Gianluca** Fiori

Dipartimento di Ingegneria dell'Informazione: Elettronica, Informatica, Telecomunicazioni, Università di Pisa

# V. Aubry-Fortuna IEF, University Paris-Sud

## **Giuseppe Iannaccone**

Dipartimento di Ingegneria dell'Informazione: Elettronica, Informatica, Telecomunicazioni, Università di Pisa

> A. Martinez University of Glasgow

**B.** Majkusiak Warsaw University of Technology

## S. Monfray

S. Reggiani ARCES, University of Bologna

C. Riddet

University of Glasgow

## J. Saint-Martin

IEF, University Paris-Sud

## E. Sangiorgi

ARCES, University of Bologna

A. Schenk ETH Zürich

L. Selmi DIEGM, University of Udine

L. Silvestri

ARCES, University of Bologna

## J. Walczak

Warsaw University of Technology

P. Palestri, C. Alexander, A. Asenov, G. Baccarani, A. Bournel, M. Braccioli, B. Cheng, P. Dollfus, A. Esposito, D. Esseni, A. Ghetti, C. Fiegna, G. Fiori, V. Aubry-Fortuna, G. Iannaccone, A. Martinez, Majkusiak B., S. Monfray, S. Reggiani, C. Riddet, J. Saint-Martin, E. Sangiorgi, A. Schenk, L. Selmi, L. Silvestri, J. Walczak, Comparison of advanced transport models for nanoscale MOSFETs, 10th International Conference on Ultimate Integration of Silicon, pp.125-128, Aachen 2009.

## Comparison of Advanced Transport Models for Nanoscale nMOSFETs

P. Palestri<sup>1</sup>, C. Alexander<sup>2</sup>, A. Asenov<sup>2</sup>, G. Baccarani<sup>3</sup>, A. Bournel<sup>4</sup>, M. Braccioli<sup>5</sup>, B. Cheng<sup>2</sup>, P. Dollfus<sup>4</sup>, A. Esposito<sup>6</sup>, D. Esseni<sup>1</sup>, A. Ghetti<sup>7</sup>, C. Fiegna<sup>5</sup>, G. Fiori<sup>8</sup>, V.

Aubry-Fortuna<sup>4</sup>, G. Iannaccone,<sup>8</sup> A. Martinez<sup>2</sup>, B. Majkusiak<sup>9</sup>, S. Monfray<sup>10</sup>, S. Reggiani<sup>3</sup>, C. Riddet<sup>2</sup>, J. Saint-Martin<sup>4</sup>, E. Sangiorgi<sup>5</sup>, A. Schenk<sup>6</sup>, L. Selmi<sup>1</sup>, L. Silvestri<sup>3</sup>, J. Walczak<sup>9</sup>, <sup>1</sup> DIEGM, University of Udine- IU.NET, Via delle Scienze 208, 33100, Udine, Italy, palestri@uniud.it

<sup>2</sup> University of Glasgow, Glasgow, UK

<sup>3</sup> ARCES, University of Bologna - IU.NET, Bologna, Italy

<sup>4</sup> IEF, University of Bologna - IU.NET, Cesena, Italy

<sup>6</sup> ETH Zürich, Gloriastrasse 35, CH-8092, Zürich. Switzerland

<sup>7</sup> Numonyx, R & D - Technology Development, Via Olivetti 2, 20041 Agrate Brianza, Italy

<sup>8</sup> University of Pisa - IU.NET, Pisa, Italy

<sup>9</sup> Warsaw University of Technology, Warsaw, Poland

<sup>10</sup> ST Microelectronics, Crolles, France

In this paper we mutually compare advanced modeling approaches for the determination of the drain current in nanoscale MOSFETs. Transport models range from Drift-Diffusion to direct solution of the Boltzmann Transport equation with the Monte-Carlo methods.

Template devices representative of 22nm Double-Gate and 32nm FDSOI transistors were used as a common benchmark to highlight the differences between the quantitative predictions of different approaches. Our results set a benchmark to assess modeling tools for nanometric MOSFETs.

#### 1. Introduction

Over the last decade, many innovative device simulation models for *lateral transport* (i.e. for the determination of the drain current  $I_{DS}$  in MOSFETs) have been developed to address the industry need to evaluate performance improvements due to quasi-ballistic transport and other technology boosters. These simulators employ a wide range of modeling approaches: from the modification of the conventional Drift-Diffusion (DD) model used in commercial TCAD tools (accounting for carrier quantization and ad-hoc mobility models for UTB-SOI, high-k stacks, strained channels) to advanced Monte-Carlo (MC) and Non-Equilibrium-Green's-Function (NEGF) simulators able to handle the strongly off-equilibrium transport taking place in decananometric devices.

A transparent and thorough assessment of these models is not trivial. Validation by direct comparison with experimental data is often unable to rule out possible model inaccuracies and implementation errors, since many parameters of the experimental devices, such as doping profiles and series resistances, which play a critical role in determining  $I_{DS}$ , are not precisely known and are used as adjusting parameters. Mutual comparison between simulations of the same devices performed with different models represent a simple and sound methodology to identify and quantify the impact of the assumptions taken by the different models. Examples of this approach are [1], [2], [3], [4]. These recent works have increased the confidence of the device community in the capabilities of device modeling.

In this paper we compare the low-field mobility data and I/V curves of template 32nm FDSOI and 22nm DG devices optimized for low-stand-by-power applications and simulated with various modeling approaches.

#### 2. Simulated Devices

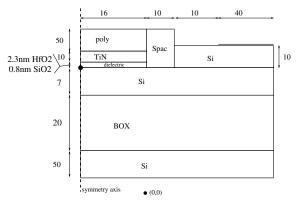

The 32nm FDSOI template is sketched in Fig.1. The channel is lowly doped  $(10^{15} \text{ cm}^{-3})$ . The substrate is p-type (N=10<sup>18</sup> cm<sup>-3</sup>). The metal work-function is 4.6eV. Doping profiles for the S/D regions have been obtained from process simulations of a realistic 32nm process.

The 22nm device is an idealized Double-Gate MOS-FET with a gate length of 22nm, a gate stack consisting of 2.4nm of  $HfO_2$  on top of 0.7nm of  $SiO_2$ (EOT=1.1nm). The silicon film thickness is 10nm and the metal work-function is 4.8eV. The doping profiles are similar to the ones of the 32nm template, with all the diffusion lengths scaled by 22/32.

Both devices are n-type and feature unstrained Si channels.

Fig. 1. Structure of the 32nm FDSOI template transistor used in this work. Only one half of the symmetric structure is reported. All dimensions are in nm. The EOT is 1.2nm.

#### 3. Simulation Approaches

In the following, the key features of each model (identified with the acronym of the main developer) are presented. For a sake of a more transparent comparison we group the models in two families: the MC family, which collects models based on the solution of the Boltzmann-Transport-Equation using the Monte Carlo method, and the DD family, which gathers driftdiffusion-like models.

#### A. MC family

**UD-MSMC:** Multi-subband ensemble Monte Carlo described in [5]. Scattering mechanisms: bulk phonons and surface roughness (SR). Ionized impurity (II) scattering in the S/D extensions is not active in these simulations, but series resistances extracted from DD simulations ( $R_S=R_D=90\Omega\mu m$  for the 22nm template and  $60\Omega\mu m$  for the 32nm one) have been introduced as lumped elements.

**BO-MC:** Full-band ensemble Monte-Carlo (free carrier gas) [6] with quantum corrections (effective potential). II scattering in the S/D calibrated to reproduce bulk mobility data for doping up to  $10^{21}$  cm<sup>-3</sup>.

**ETH-MC:** Full-band ensemble Monte Carlo with phonon, II and SR scattering [7]. The scattering physics is the same as in [8]. Quantum correction not taken into account. SR is included using partially diffusive scattering at the SiO<sub>2</sub> interface with a Fuchs factor of 20%. **Numonyx-MC:** Full-Band ensemble Monte-Carlo (free carrier gas) [9] with quantum correction of the potential computed by solving self-consistently the Schrödinger equation in 1D slices of the device. Scattering mechanisms include: elastic acoustic phonon, inelastic optical phonon, II (isotropic model of [8]), impact ionization, SR (treated as in [10]).

**IEF-MC:** Ensemble Monte Carlo with ellipsoidal analytical bands (free carrier gas) [11]. Quantum corrections are not taken into account here. Scattering mechanisms include: phonons, II and SR (14% fraction of diffusive scattering at SiO<sub>2</sub> interface) [12].

**UGLA-MC:** 3D Monte Carlo simulator [13]. An efficient methodology is used for the self-consistent inclusion of 3D density gradient quantum corrections [14]. The simulator is specifically designed to study current variability associated with the randomness of different scattering sources.

#### B. DD family

**BO-QDD:** quantum drift diffusion, (1D drift-diffusion combined with the solution of the coupled Schrödinger-Poisson equations on the device cross-sections normal to the transport direction) [15]. Mobility model described in [16].

**UGLA-aDD:** drift diffusion *atomistic* simulator specially designed for statistical simulation of atomic scale variability. It employs density gradient quantum corrections [17]. In this work, the aDD has been calibrated on Dessis simulations with standard mobility models for impurity scattering, and for the lateral and vertical field mobility dependence.

**PI-MSDD:** Multi-subband DD, i.e. self-consistent solution of the 2D Poisson and Schrödinger equations (in the direction perpendicular to the Si/SiO2 interface), coupled with the solution of the continuity equation along subbands in the DD approximation [18], [19]. The low field mobility of [20] has been implemented, while the approach described in [21] has been adopted for high electric fields.

#### C. Others

**UGLA-NEGF:** Modified version [22] of the fully 2D NEGF simulator initially developed by NASA [23]. **WUT:** Mobility model based on the relaxation time approximation, including bulk phonons, SR, and Coulomb scattering. The SR model is based on Ando's

approach, modified to include SOI-specific effects [24].

#### D. Model calibration

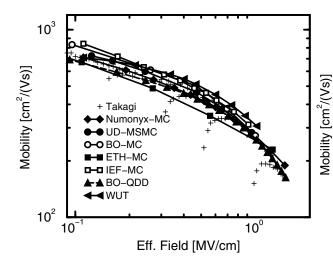

Models differ in terms of band-structure, scattering models, treatment of non-local transport, etc. For a sake of a fair comparison, all simulators have been first calibrated to reproduce the universal curves in bulk Si devices (see Fig.2).

Not all models contain all the ingredients needed to simulate advanced devices as the template transistors defined in Sec.2. In particular, some can handle strain but not high-k stacks, and so on. Furthermore, scattering models for options such as high-k dielectrics are not well assessed and established [25]. For these reasons, although the template devices include high-k stacks, and although 32nm and 22nm devices are likely to include strained channels, in this work we consider unstrained Si channels and neglect the scattering mechanisms induced by the presence of the high-k dielectric.

Fig. 2. Simulated low-field mobility in bulk devices in the absence of II scattering, showing the calibration of the transport parameters.

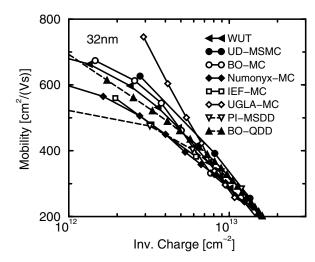

Fig. 3. Low-field mobility of the 32nm FDSOI template.

#### 4. Results

#### A. Low-Field Mobility

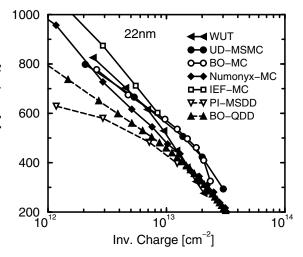

We report in Figs.3,4 the low-field mobility as computed in long channel devices with the same *vertical* structure as the templates. The mutual agreement between the different models is quite good at large  $N_{\rm inv}$ , whereas discrepancies appear at low  $N_{\rm inv}$ , especially in the 22nm DG device.

#### B. Current in the 32nm template

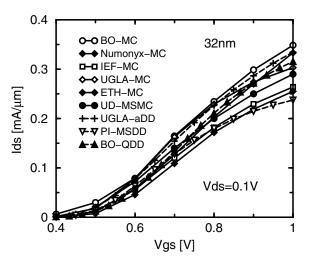

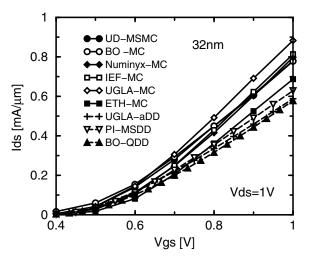

Figs.5,6 report I/V curves of the 32nm FDSOI template. Considering the models of the DD family, the figures show a more than satisfactory mutual agreement, that was observed also below threshold (not shown).

Considering now MC simulations, these models are expected to take into account more accurately the quasiballistic nature of carrier transport in short MOSFETs. The mutual agreement is quite satisfactory, much better of what has been found in [4], mainly because in

Fig. 4. Low-field mobility of the 22nm DG template.

Fig. 5. Trans-characteristics of the 32nm FDSOI template for  $V_{DS}$ =0.1V. In this figure and in the following ones, in the MC simulations II scattering is active in the S/D regions.

Fig. 6. Trans-characteristics of the 32nm FDSOI template for  $V_{DS}$ =1V.

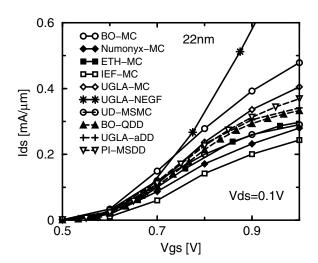

Fig. 7. Trans-characteristics of the 22nm DG template for  $V_{DS}$ =0.1V.

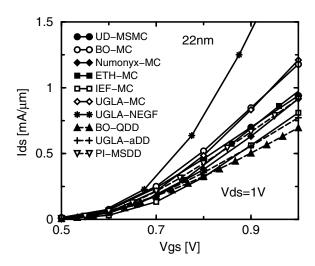

Fig. 8. Trans-characteristics of the 22nm DG template for  $V_{DS}$ =1V.

the devices considered in this work the role of II scattering in the S/D regions is significantly reduced with respect to the devices in [4]. As expected, the current provided by the MC models is larger than the one given by the DD ones at high  $V_{DS}$ , where non-equilibrium effects become significant. At low  $V_{DS}$ , instead, the two approaches give essentially the same current

#### C. Current in the 22nm DG template

Comparisons between the MC, DD and NEGF results for the 22nm DG template are reported in Figs.7,8. Concerning the DD models, the overall agreement is as good as for the 32nm device.

Concerning the MC models, at low  $V_{DS}$  the agreement between  $I_{DS}$  predictions is quite poor, but it improves for  $V_{DS}$ =1V. Possible explanations can be traced back to the different modeling of SR and phonon scattering in thin film Double-Gate SOI structures.

Mutual comparison between DD, MC and NEGF simulators for both templates is summarized in Table.I.

| Dev. | $V_{DS}$ | DD   | MC (II) | MC (no-II) | NEGF |

|------|----------|------|---------|------------|------|

| 22nm | 0.1      | 0.3  | 0.3     | 0.6        | 0.85 |

| 22nm | 1.0      | 0.7  | 1.0     | 1.3        | 2.3  |

| 32nm | 0.1      | 0.3  | 0.3     | 0.45       | n.a. |

| 32nm | 1.0      | 0.55 | 0.8     | 0.9        | n.a. |

Comparison between DD, MC and NEGF  $I_{DS}$  values (mA/ $\mu$ m) for  $V_{GS}$ =1V. The data are averages between the results reported in the previous figures.

We see that: a) DD and MC models provide quite close  $I_{DS}$  at low  $V_{DS}$ ; b) ionized impurity scattering in the S/D is important, especially at low  $V_{DS}$ ; c) ballistic NEGF solvers significantly overestimates the  $I_{DS}$  of these nanoscale devices.

#### 5. Conclusions

The comparison presented in this work has interested four DD simulators, six MC simulators and one NEGF solver. The model predictions tend to converge for longer channel devices (especially when considering the DD models), whereas the predictions of the scaling trends of Ion improvement in short devices are quantitatively quite different among the models. Comparison with ballistic NEGF results, points out that even with the limited number of scattering mechanisms accounted for in this work (II, phonons, SR) scattering still plays a remarkable role in decenanometric devices. The impact of scattering on Ion may become even larger if specific mechanism (e.g. remote phonons and remote charges in the high-k) are included in the models.

#### Acknowledgments: PULLNANO project, IST-026828.

#### References

- [1] A. Abramo et al., IEEE T-ED, v.41, p.1646, 1994

- [2] C.A. Ritcher et al., IEEE EDL, v.22, p. 25, 2001

- [3] P. Palestri et al., IEEE T-ED, v.54, p.106, 2007

- [4] C. Fiegna et. al., SISPAD 2007, p.57

- [5] L. Lucci et al., IEEE T-ED, v.54, p.1156, 2007

- [6] P. Palestri et al., Solid State Elect., v.49, p.727, 2005

- [7] S.C. Brugger, Series in Microelectronics, Vol. 166, 2006.

- [8] F. M. Bufler et al., IEEE T-ED, v.47, p.1891, 2000.

- [9] A. Ghetti, D. Rideau, SISPAD 2006, p.67.

- [10] A.T.Pham et al., Solide-State Elect., v.50, p.694, 2006

- [11] D. Querlioz et al., IEEE T-ED. v.54, p.2232, 2008

- [12] V. Aubry-Fortuna et al., Semic. Sci. Tech., v.21, p.422, 2006

- [13] C. Alexander et al., IEEE T-ED. v.55, 2008.

- [14] C. Riddet and A. Asenov, SISPAD 2008.

- [15] G. Baccarani et al., Solid-State Elect., v.52, p.526, 2008.

- [16] S. Reggiani et al., IEDM 2007, p.557.

- [17] G. Roy et al., IEEE T-ED. v.52, p.3063, 2006.

- [18] G. Curatola et al., IEEE T-ED, v.52, p.1851, 2005.

- [19] G. Fiori et al., IEEE T-NANO, v.6, p.524, 2007.

- [20] S. Reggiani et al., IEEE T-ED, v.54, p.2204, 2007.

- [21] M. N. Darwish et al., IEEE T-ED, v.44, p.1529, 1997.

- [22] A. Martinez et al., IEEE T-NANO, v.6, p.438, 2007.

- [23] A. Svizhenko et al., J. App. Phys., v. 91, p.2343, 2002.

- [24] S. Jin et al., IEEE T-ED, v.54, p.2197, 2007.

- [25] P.Toniutti et al., ESSDERC 2008