#### **CMOS** Manufacturing process

All material: Chap. 2 of J. Rabaey, A. Chandrakasan, B. Nikolic, Digital Integrated Circuits, second edition, Prentice Halls, 2002

#### **Simplified very basic CMOS Process**

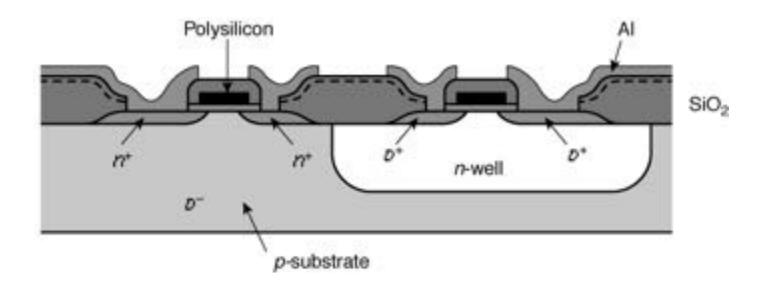

CMOS inverter – n-well process

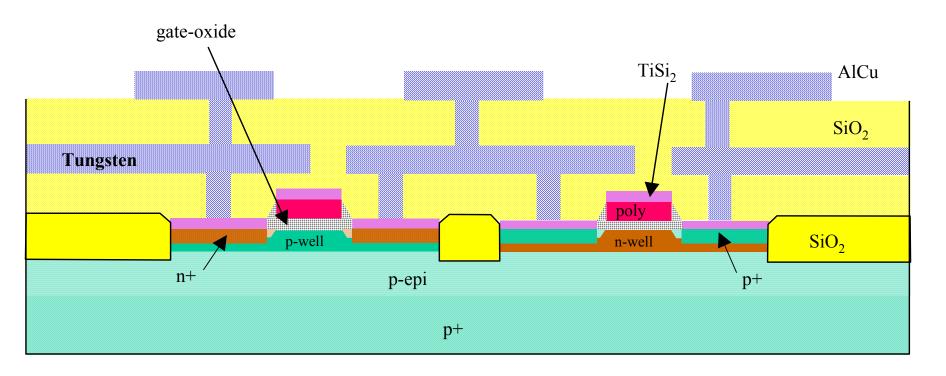

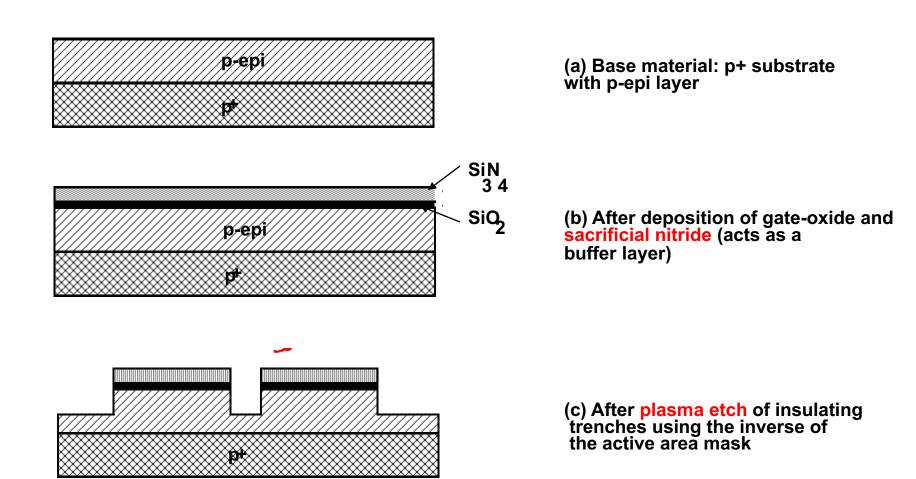

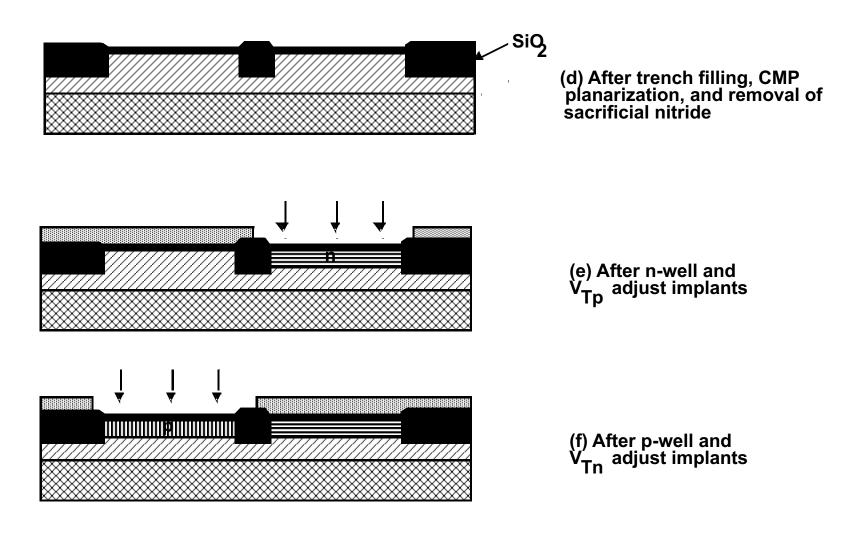

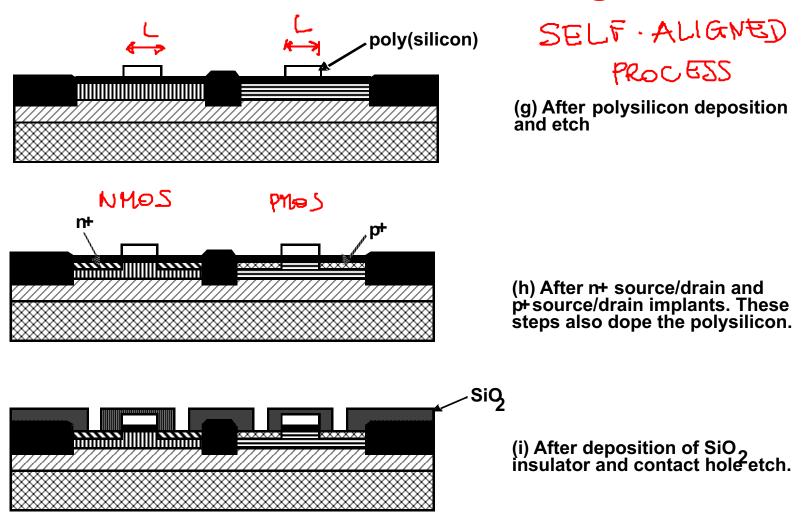

#### **A Modern CMOS Process**

CMOS inverter – dual-well trench-isolated process

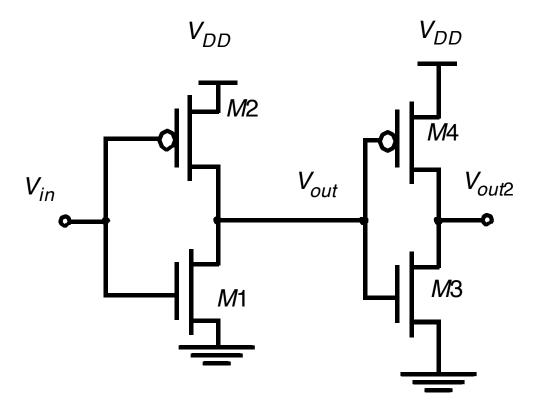

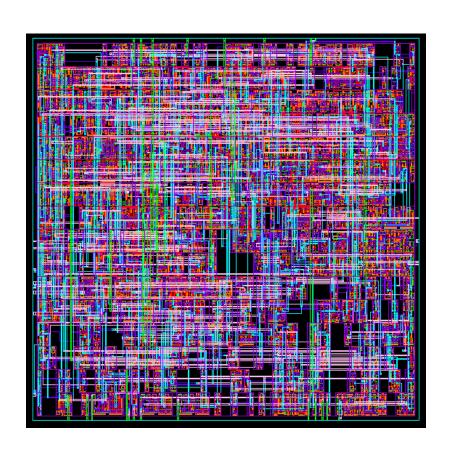

# **Circuit Under Design**

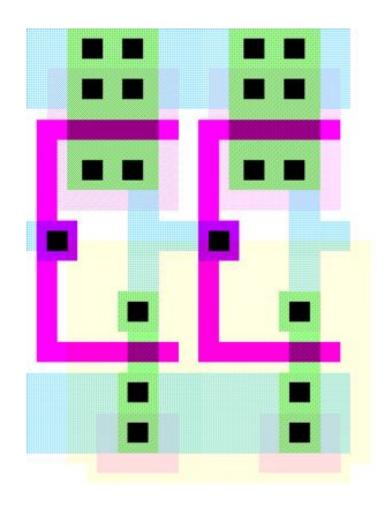

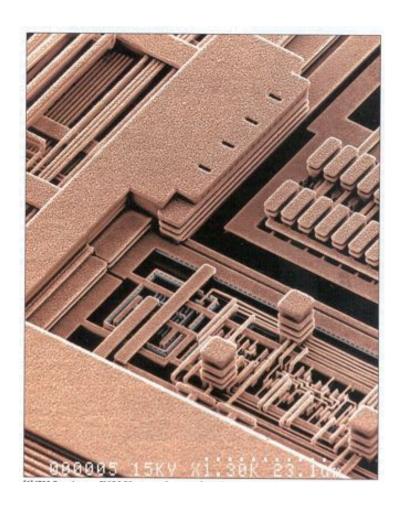

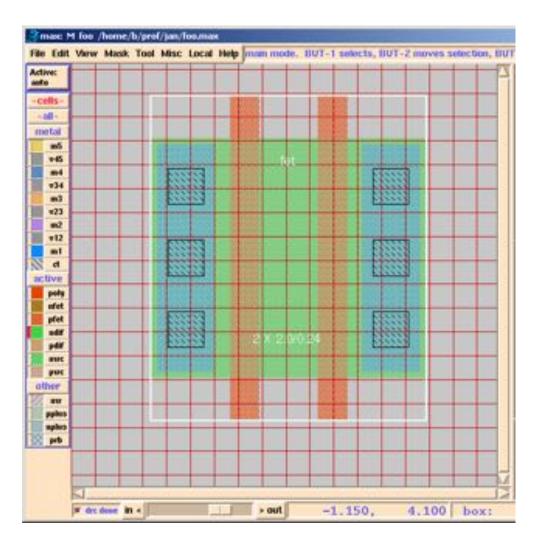

## **Its Layout View**

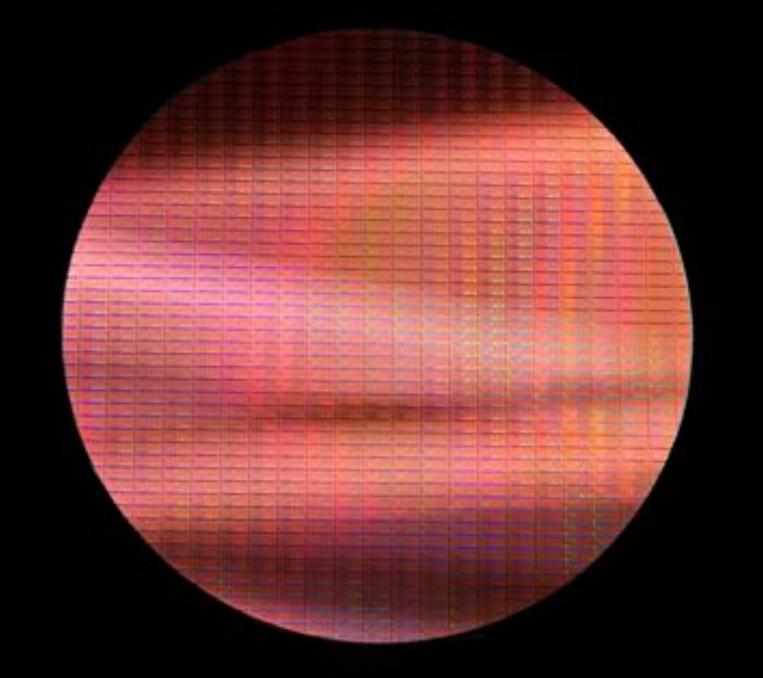

## Silicon ingot

Diameter 12 inches (300 mm)

Weight 100 Kg

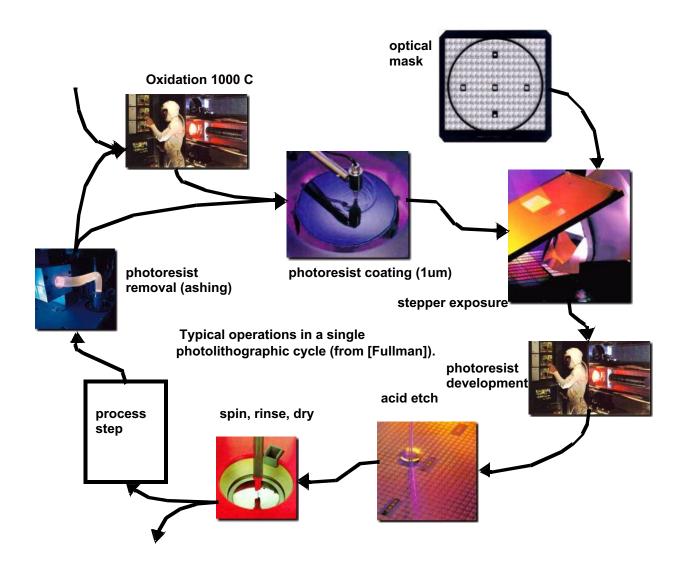

#### **Photo-Lithographic Process**

Clean room (class 1-10)

Def:

Class 1:

<1 dust

particle per

cubic foot

In each processing step, an area of the chip is masked out using optical masks, so that the process step is selectively applied to the other regions

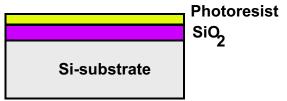

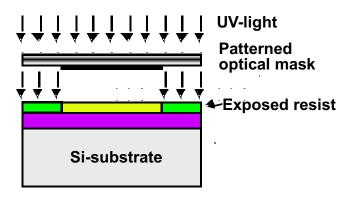

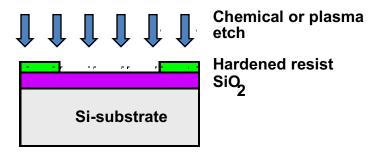

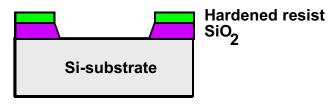

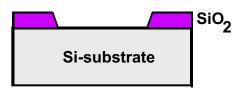

# **Example of process step:**Patterning of SiO2

Si-substrate

(a) Silicon base material

(b) After oxidation and deposition of negative photoresist

(c) Stepper exposure

(d) After development and etching of resist, chemical or plasma etch of SiO<sub>2</sub>

(e) After etching

(f) Final result after removal of resist

### Recurring process steps (1/2)

- Doping

- Diffusion (gas with dopant, 900-1100 °C)

- Ion implantation

- Lattice damage (displacement of atoms)

- → Annealing step (1000 °C for 15-30′ + slow cooling)

- Deposition (of layers over the complete wafer)

- Oxidation [silicon oxide]

- Chemical Vapor Deposition: gas phase + heat (850 °C)

[silicon nitride]

- Chemical deposition (polysilicon: silane (SiH₄) gas over heated wafer (600 °C) → reaction an polysilicon formation

- Sputtering (for aluminum): evaporation in vacuum chamber

### Recurring process steps (2/2)

- Etching (defines 3D patterns on the surface)

- Wet etching (with acid or basic solutions)

- e.g. Hydrofluoric acid for silicon oxide

- Almost isotropic

- Dry or plasma etching

- Plasma: mix of nitrogen, chlorine, boron trichloride

- Strongly anisotropic (steep vertical edges)

- Planarization (flatten the surface to allow layer deposition)

- Chemical Mechanical Polishing (CMP)

- Liquid carrier with a suspended abrasive component

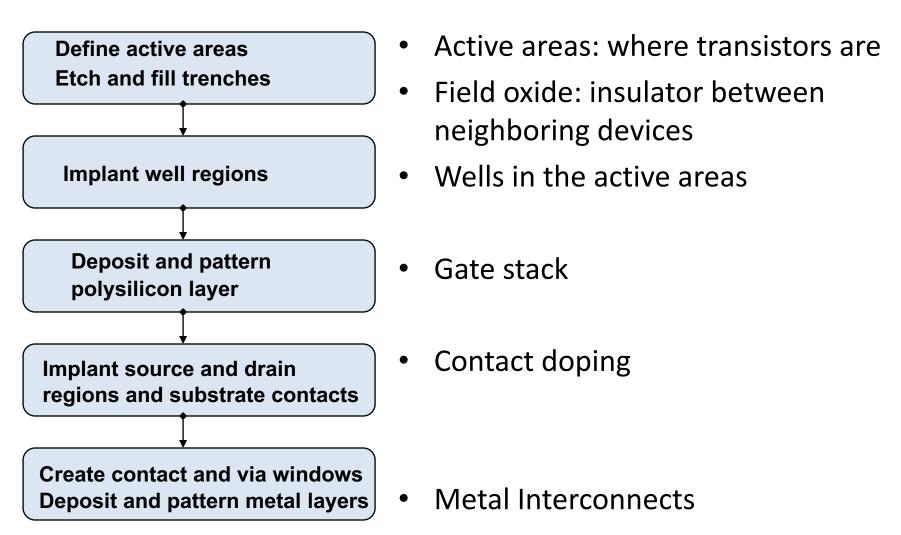

### **Simplified CMOS Process flow**

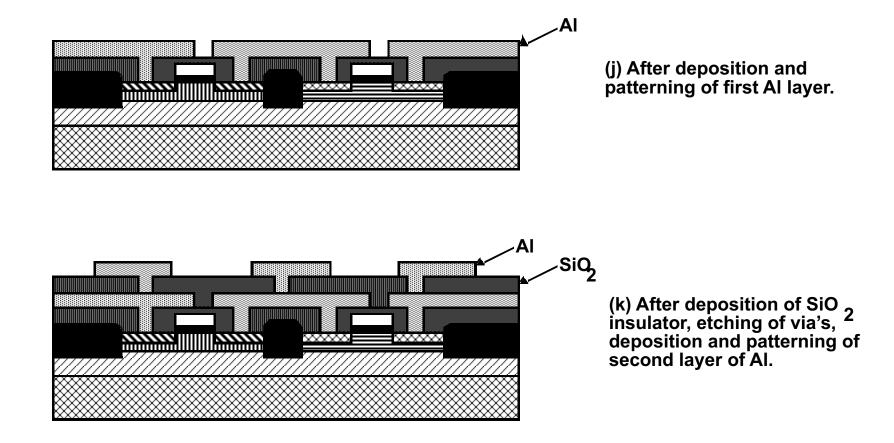

#### **Advanced Metallization**

#### **CMOS** Manufacturing process

All material: Chap. 2 of J. Rabaey, A. Chandrakasan, B. Nikolic, Digital Integrated Circuits, second edition, Prentice Halls, 2002

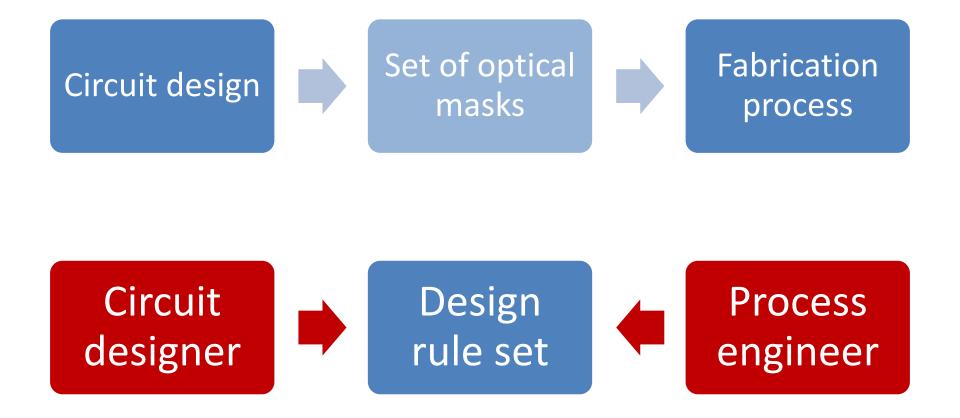

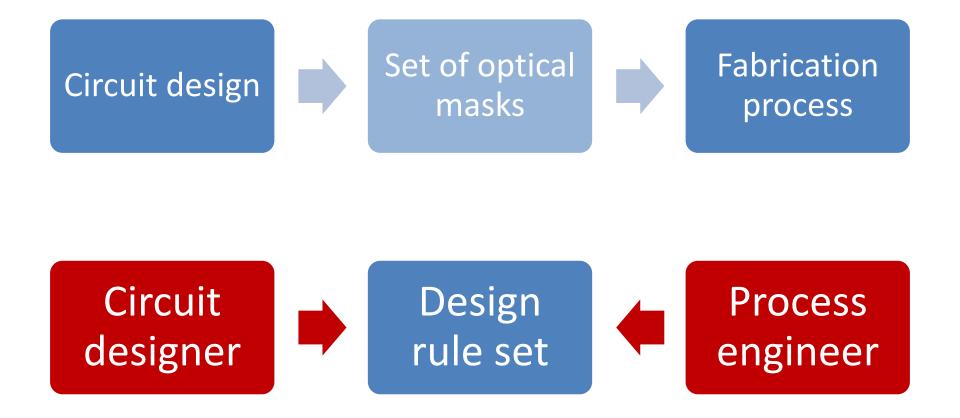

#### **Design Rules**

Minimum line width depend on lithography and process

• Micron rules: absolute dimensions for intra-layer and inter-layer layouts

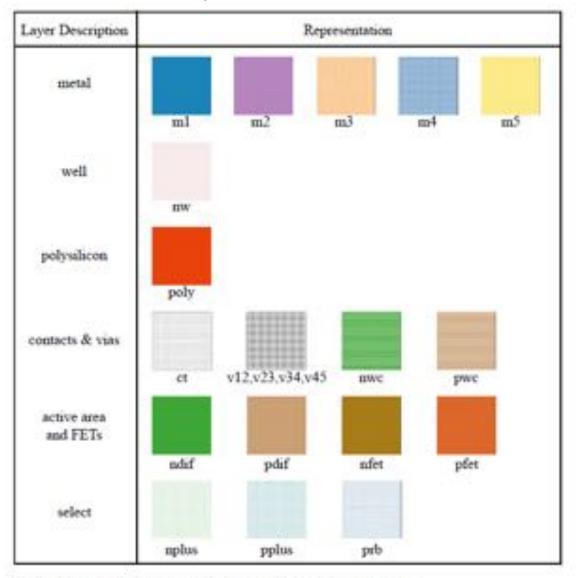

## Layers in 0.25 µm CMOS process

Colorplate 1. CMOS layers and representations (for vanilla 0.25 µm CMOS process)

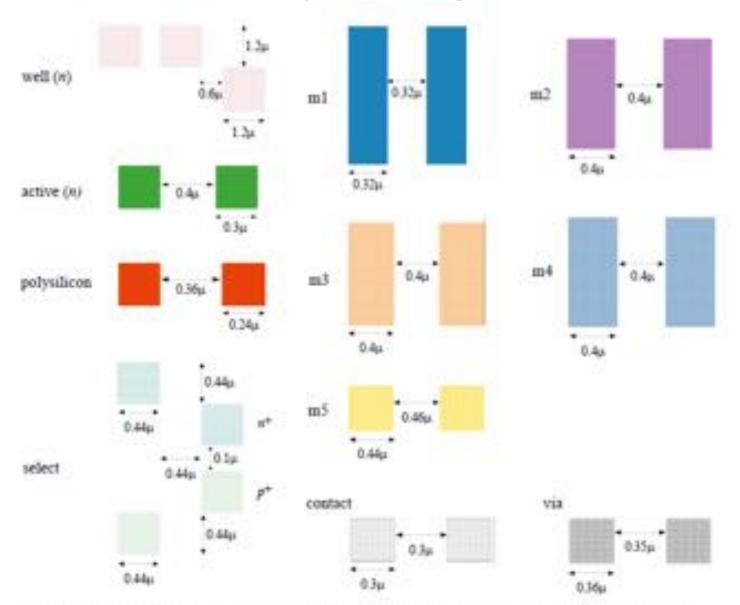

#### **Intra-Layer Design Rules**

Colorplate 2. Intra-layer layout design rules, expressed as minimum dimensions and spacings.

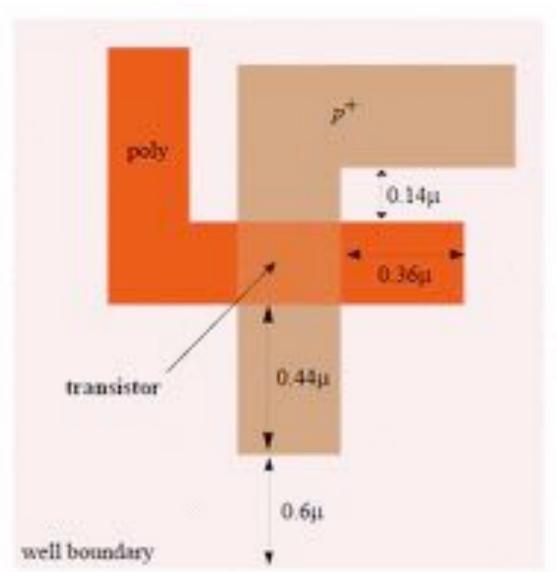

#### **Transistor Layout**

Colorplate 3. Design rules concerning transistor layout. The device shown is a PMOS transistor.

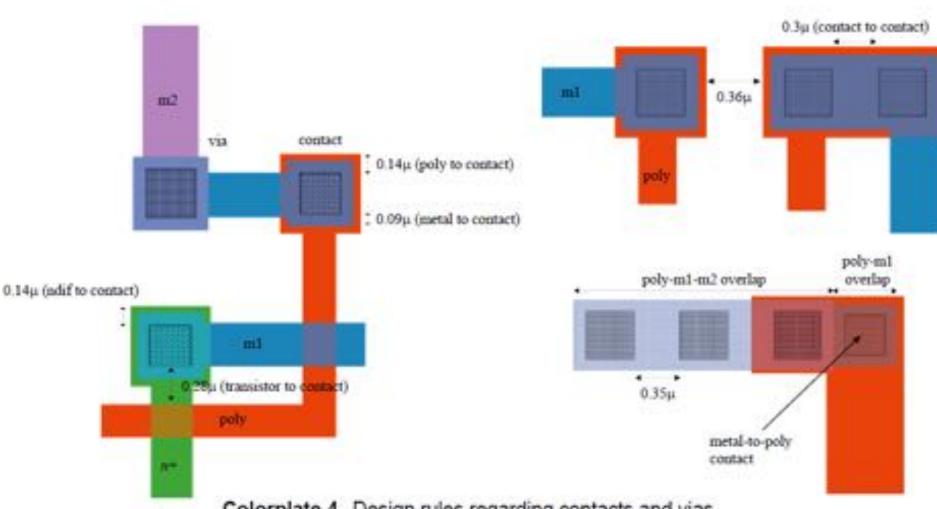

#### **Vias and Contacts**

Colorplate 4. Design rules regarding contacts and vias. Overlapping layers are marked by merged colors.

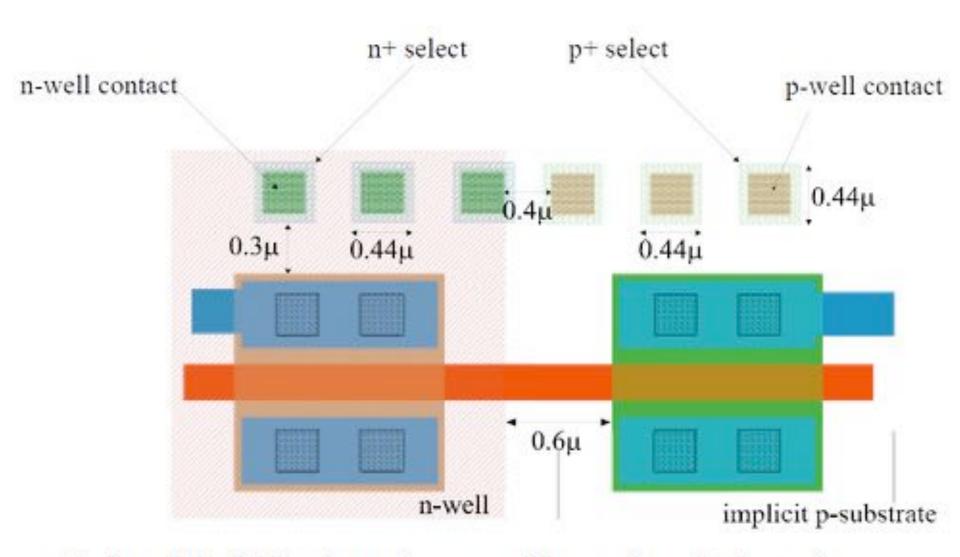

#### **Select Layer**

Colorplate 5. Design rules regarding well contacts and select layers.

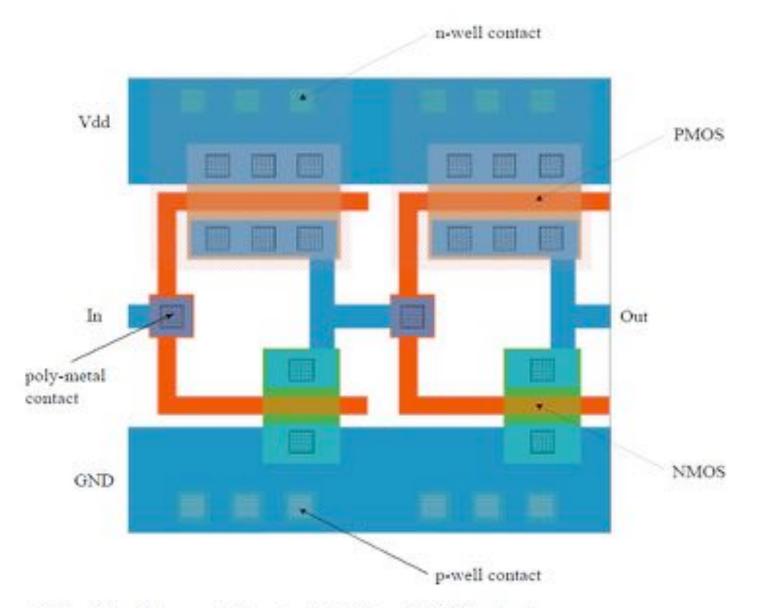

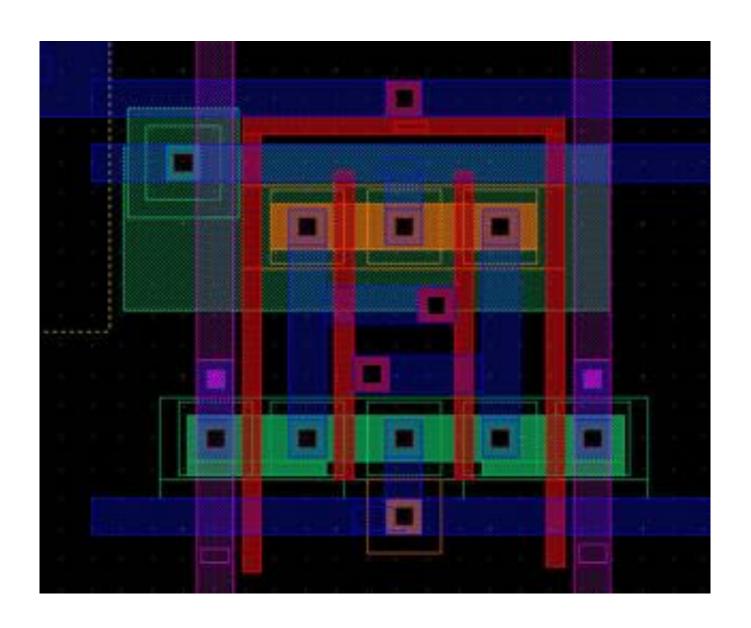

#### **CMOS Inverter Layout**

Colorplate 6. Layout of inverter in 0.25 µm CMOS technology.

## **Layout Editor**

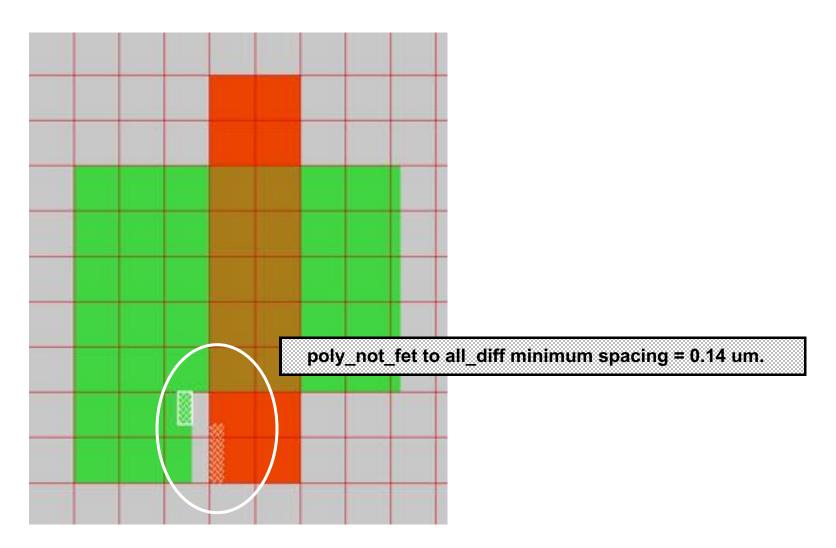

## **Design Rule Checker**

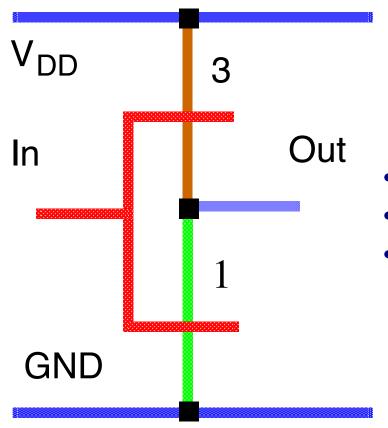

#### **Sticks Diagram**

- Dimensionless layout entities

- Only topology is important

- Final layout generated by "compaction" program

Stick diagram of inverter

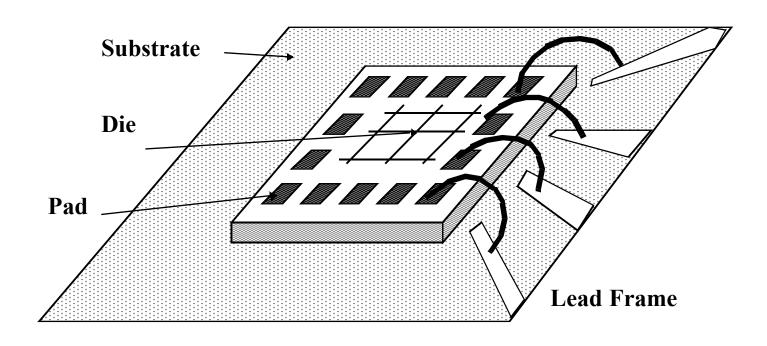

#### **Packaging Requirements**

- Electrical: Low parasitics

- Mechanical: Reliable and robust

- Thermal: Efficient heat removal

- Economical: Cheap

## **Bonding Techniques**

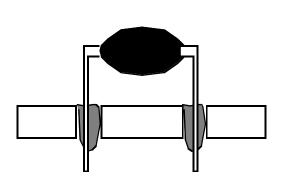

#### **Wire Bonding**

Gold wires, large inductance

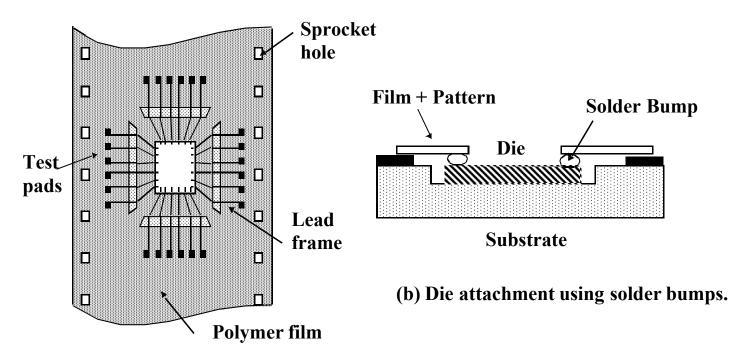

#### **Tape-Automated Bonding (TAB)**

(a) Polymer Tape with imprinted wiring pattern.

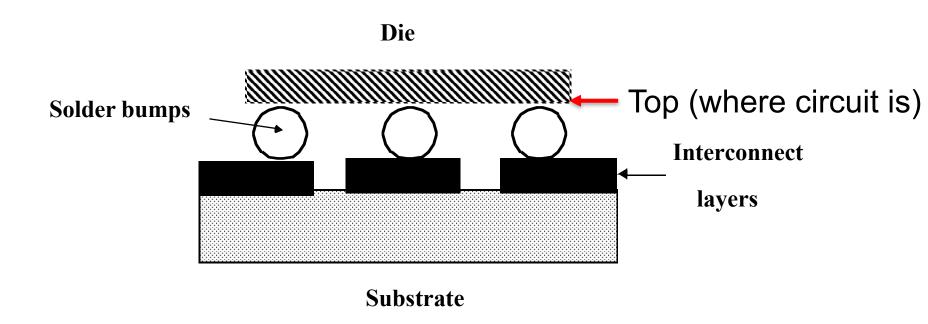

#### Flip-Chip Bonding

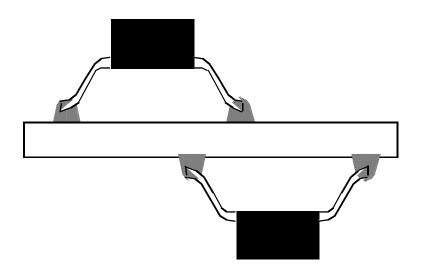

### **Package-to-Board Interconnect**

(a) Through-Hole Mounting

(b) Surface Mount

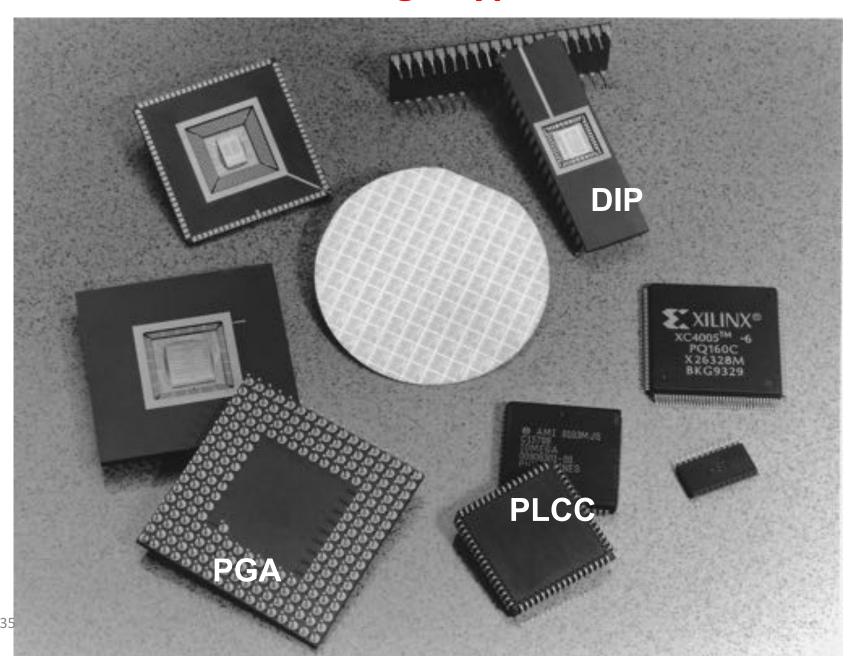

## **Package Types**

#### **Package Parameters**

| Package Type           | Capacitance<br>(pF) | Inductance<br>(nH) |

|------------------------|---------------------|--------------------|

| 68 Pin Plastic DIP     | 4                   | 35                 |

| 68 Pin Ceramic DIP     | 7                   | 20                 |

| 256 Pin Pin Grid Array | 5                   | 15                 |

| Wire Bond              | 1                   | 1                  |

| Solder Bump            | 0.5                 | 0.1                |

Typical Capacitances and Inductances of Various Package and Bonding Styles (from [Sze83])

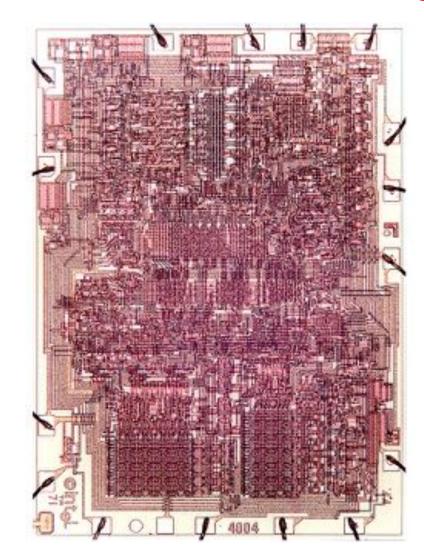

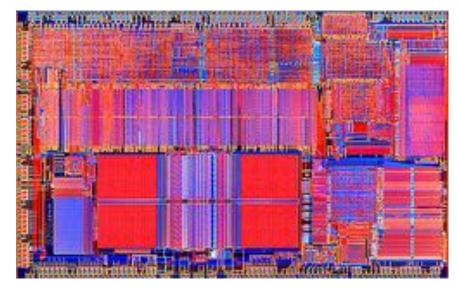

### Intel 4004 – custom design

2300 PMOS

$10 \ \mu m \ process$

Clock: 108 KHz

Area:

3 mm x 4 mm

Courtesy Intel

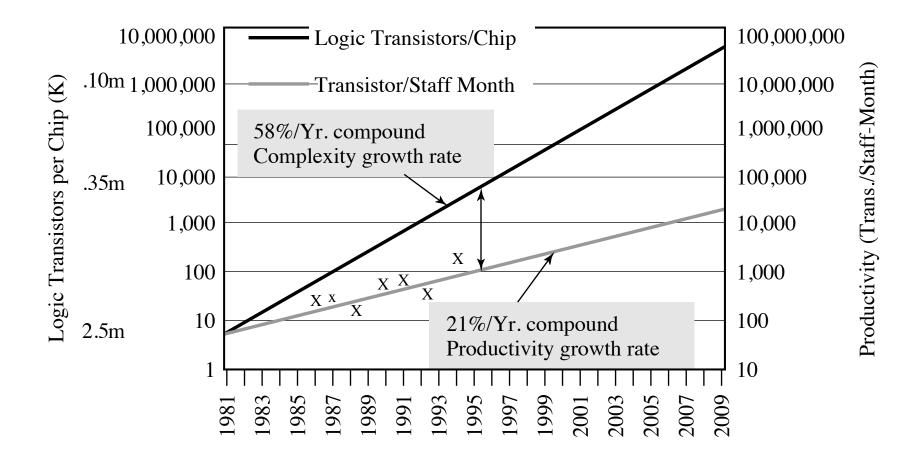

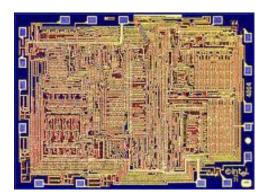

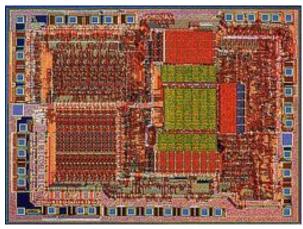

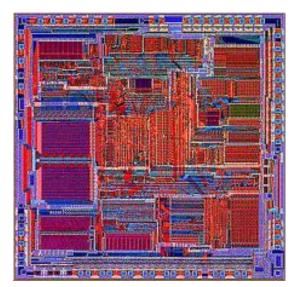

# Transition to Automation and Regular Structures

Intel 4004 ('71)

Intel 8080

Intel 8085

**Intel 8286**

Intel 8486

Courtesy Intel

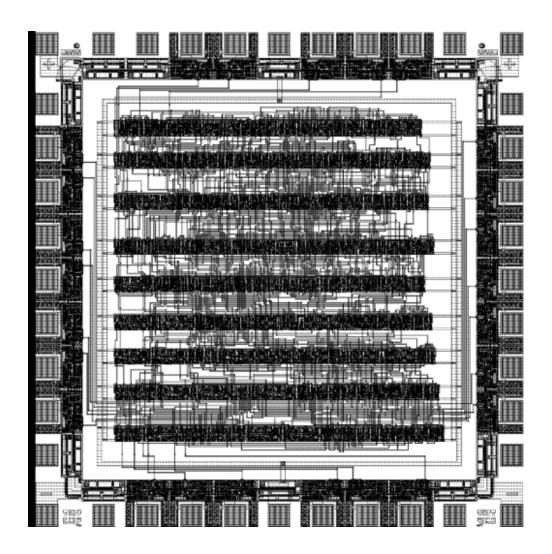

## **Standard Cell — Example**

[Brodersen92]

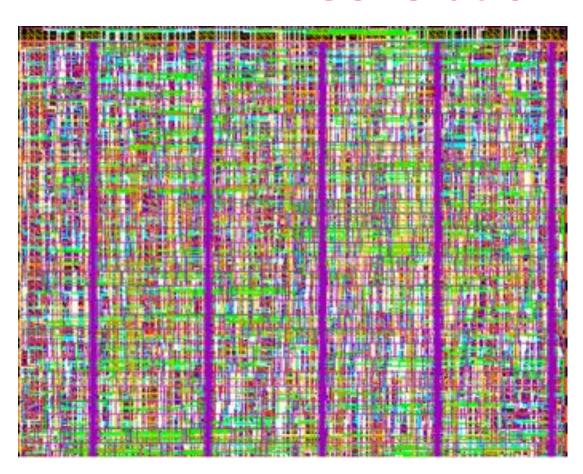

# Standard Cell – The New Generation

Cell-structure hidden under interconnect layers

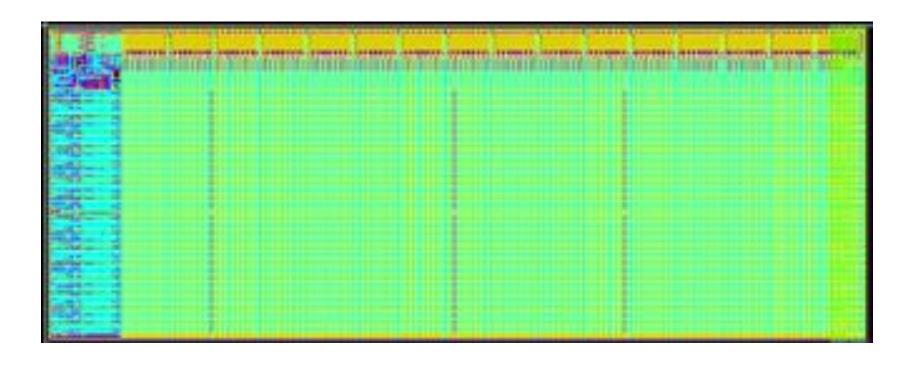

#### **MacroModules**

256×32 (or 8192 bit) SRAM Generated by hard-macro module generator

# "Soft" MacroModules

```

string mat = "booth";

directive (multtype = mat);

output signed [16] Z = A * B;

```

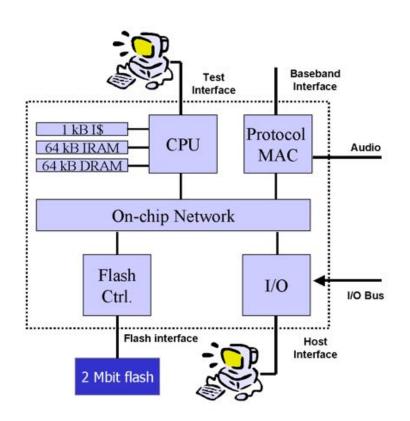

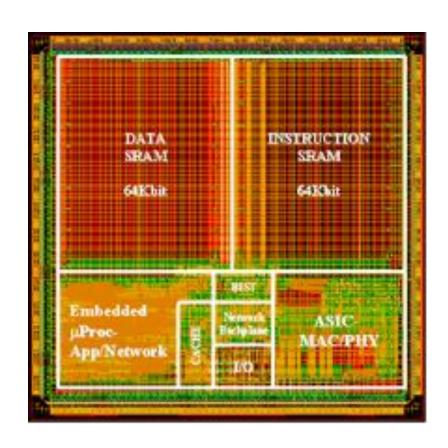

# "Intellectual Property"

A Protocol Processor for Wireless

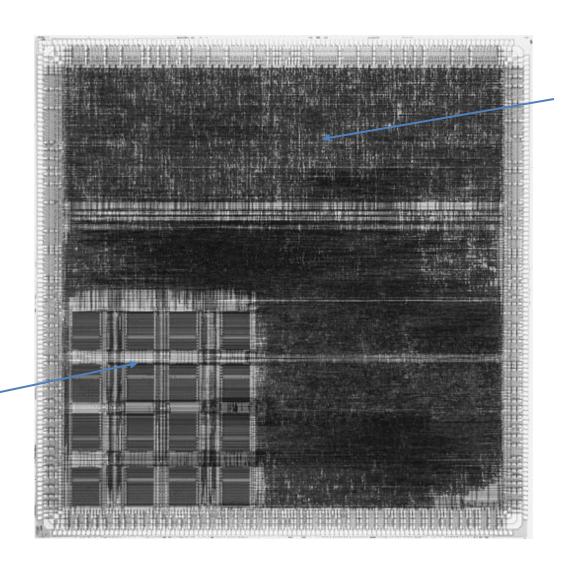

### **Sea-of-gates**

Random Logic

Memory - Subsystem

LSI Logic LEA300K (0.6 µm CMOS)

Courtesy LSI Logic

## **RAM-based FPGA**

Xilinx XC4000ex

### **Xilinx Virtex UltraScale**

| Value                              | Deliverables                                                                                                                                                                                                                                                                        |  |  |  |  |  |

|------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Programmable System<br>Integration | <ul> <li>Up to 5.5M System Logic Cells at 20nm using 2<sup>nd</sup> generation 3D IC</li> <li>Integrated 100G Ethernet MAC and 150G Interlaken cores</li> </ul>                                                                                                                     |  |  |  |  |  |

| Increased System Performance       | <ul> <li>Up to two speed-grade improvement with high utilization</li> <li>30G transceivers for chip-to-chip, chip-to-optics, 28G backplanes</li> <li>16G backplane capable transceivers at half the power</li> <li>2,400 Mb/s DDR4 for robust operation over varying PVT</li> </ul> |  |  |  |  |  |

| BOM Cost Reduction                 | Up to 50% lower cost – half the cost per port for Nx100G systems VCXO and fractional PLL integration reduces clocking component cost 2,400 Mb/s DDR4 in a mid-speed grade                                                                                                           |  |  |  |  |  |

| Total Power Reduction              | Up to 40% lower power vs. previous generation Fine granular clock gating with ASIC-like clocking Enhanced logic cell packing reduces dynamic power                                                                                                                                  |  |  |  |  |  |

| Accelerated Design<br>Productivity | <ul> <li>Footprint compatibility with Kintex UltraScale devices for<br/>scalability</li> <li>Seamless footprint migration from 20nm planar to 16nm FinFET</li> <li>Co-optimized with Vivado Design Suite for rapid design closure</li> </ul>                                        |  |  |  |  |  |

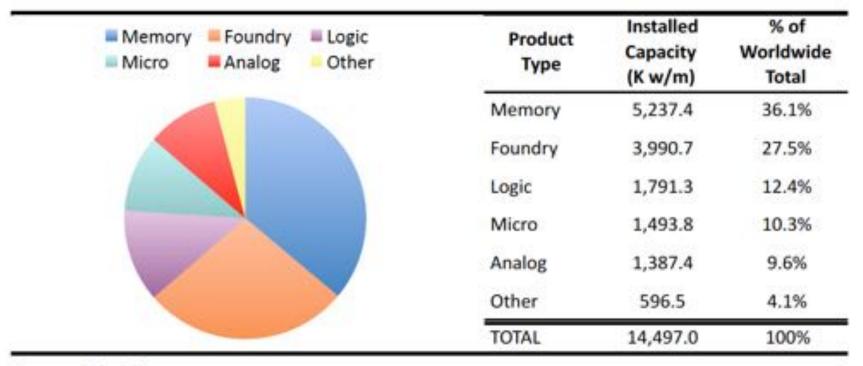

### **IC Production – Installed capacity**

Worldwide Capacity by Product Type as of Dec-2012 (Installed Monthly Capacity in 200mm-Equiv. Wafers x1000)

Source: IC Insights

# IC Production Breakdown by Region

Regional Capacity by Product Type as of Dec-2012 (Installed Monthly Capacity in 200mm-Equiv. Wafers x1000)

| Product | Americas | Europe  | Japan   | Korea   | Taiwan  | China   | ROW     | Total    |

|---------|----------|---------|---------|---------|---------|---------|---------|----------|

| Analog  | 323.5    | 328.3   | 391.9   | 31.5    | 19.2    | 153.5   | 139.4   | 1,387.4  |

| Memory  | 382.9    | 29.3    | 1,109.1 | 1,821.8 | 1,194.3 | 338.3   | 362.0   | 5,237.4  |

| Logic   | 341.1    | 167.8   | 704.2   | 363.1   | 37.7    | 70.9    | 106.5   | 1,791.3  |

| Micro   | 727.2    | 326.4   | 251.1   | 26.3    | 5.1     | 11.2    | 146.6   | 1,493.8  |

| Foundry | 296.5    | 135.5   | 124.5   | 254.6   | 1,899.0 | 737.3   | 543.3   | 3,990.7  |

| Other   | 50.0     | 128.5   | 119.2   | 67.5    | 10.1    | 19.8    | 201.3   | 596.5    |

| Total   | 2,121.3  | 1,115.7 | 2,700.1 | 2,564.7 | 3,165.4 | 1,330.8 | 1,499.0 | 14,497.0 |

Source: IC Insights

Korea, Japan ~ 2x Europe Taiwan ~ 3x Europe

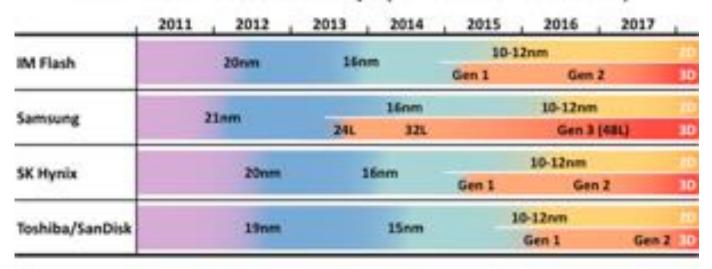

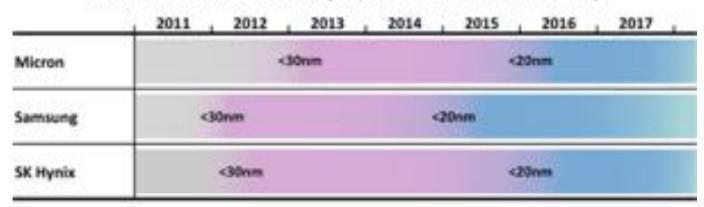

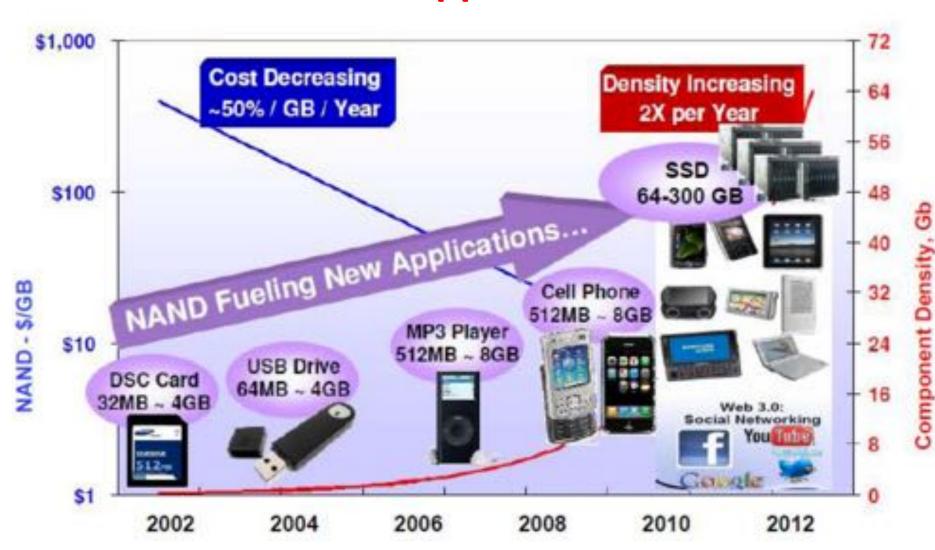

### **Memory roadmap**

#### NAND Flash Process Roadmaps (for Volume Production)

#### DRAM Process Roadmaps (for Volume Production)

Note: What defines a process "generation" and the start of "volume" production varies from company to company, and may be influenced by marketing embelishments, so these points of transition should be used only as very general guidelines.

Sources: Companies, conference reports, IC Insights:

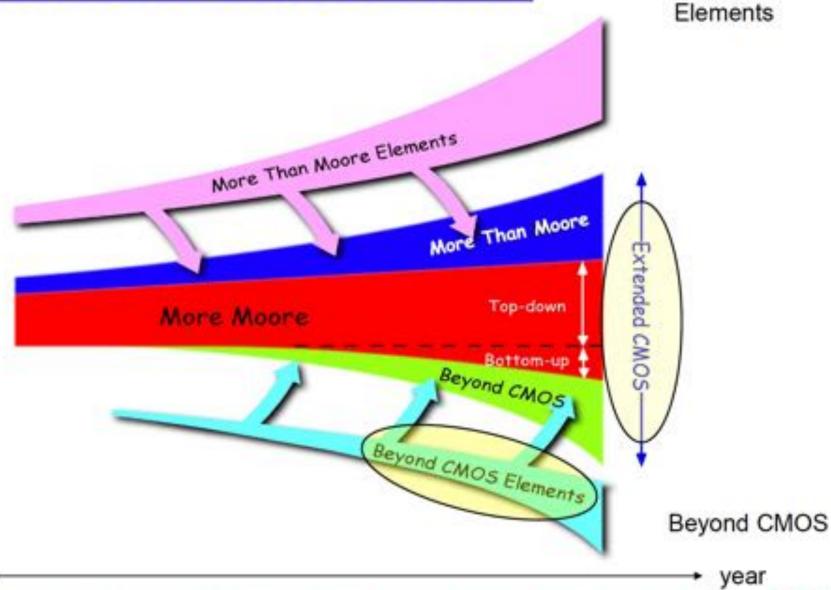

## **Evolution of Extended CMOS**

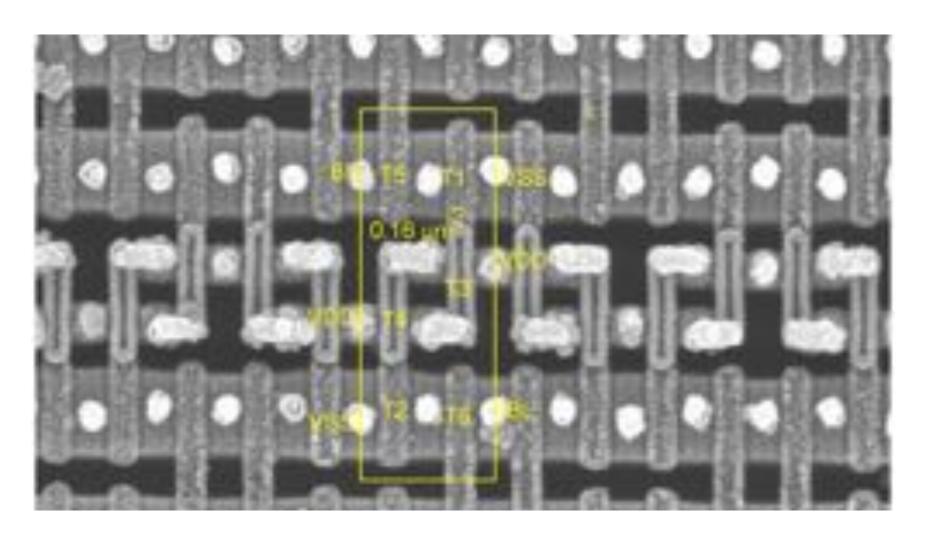

## **SRAM Layout**

#### 6T SRAM – 28 nm CMOS TSMC

**Courtesy of Chipworks**

#### **NVM Applications**

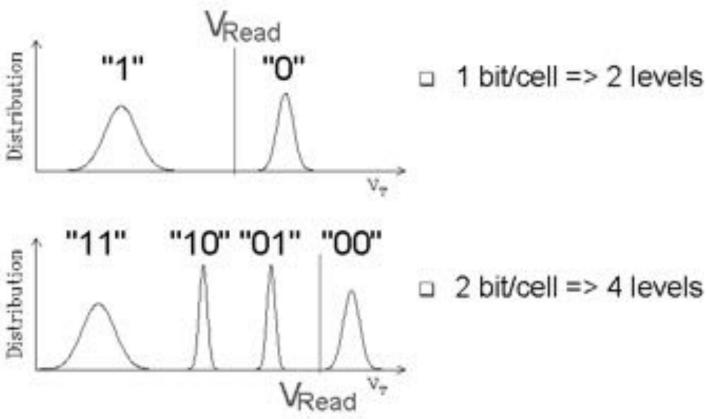

### Multilevel concept: 1

Threshold voltage distribution

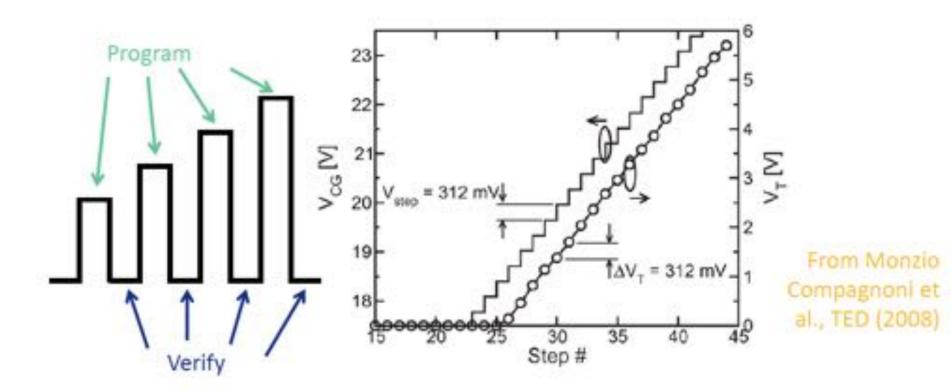

# Multilevel concept: Program and verify mechanism

$$\Delta V_T = V_{step}$$

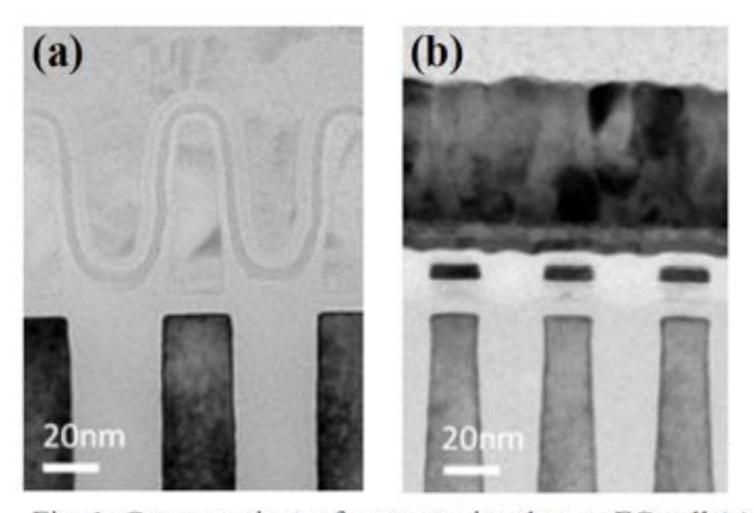

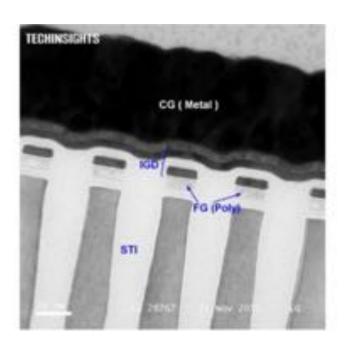

#### NAND: From gate wrap to 2D planar

Fig. 1: Cross-sections of a conventional wrap FG cell (a) and an Intel-Micron 20nm planar FG cell (b).

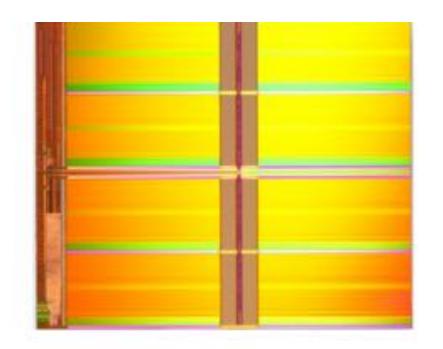

#### 2012

- 8 GB IMFT NAND Flash

- 20 nm technology node

- More than 32 billion MOS devices in 118 mm<sup>2</sup>

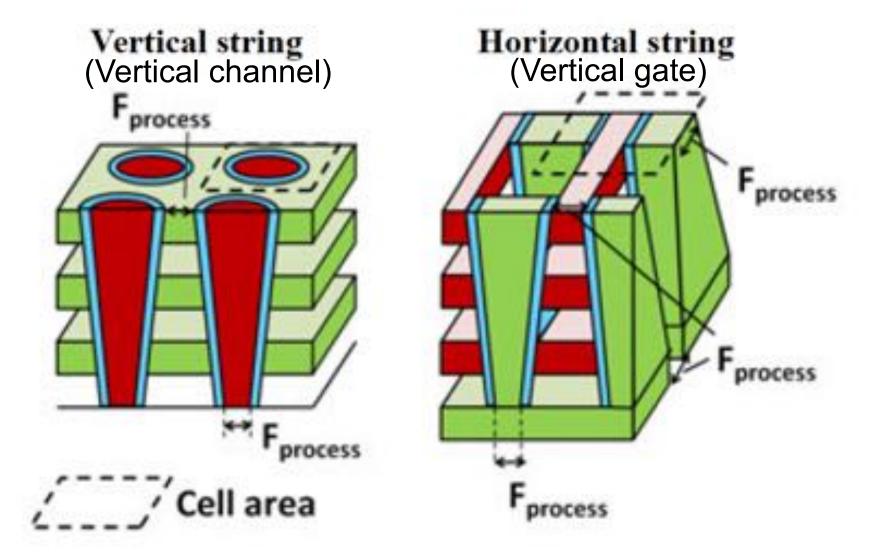

#### **Now: 3D NAND Architectures**

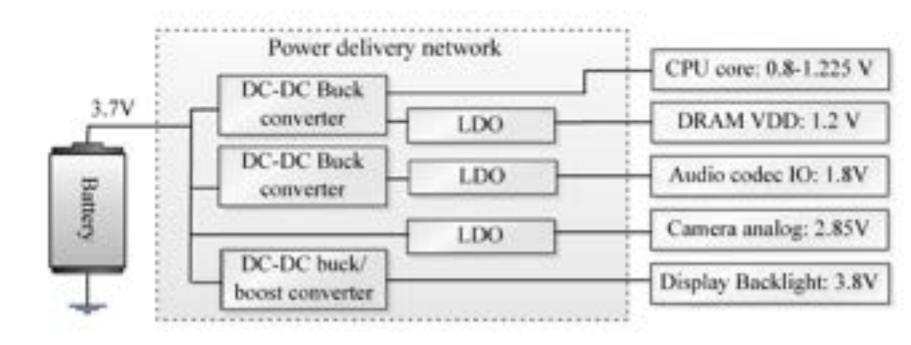

### **Power Delivery Network of a Smartphone**

Fig. 1. Conceptual diagram of the PDN in a smartphone platform.

Lee et al., IEEE-TCAD Vol.33, pp, 136, 2015.

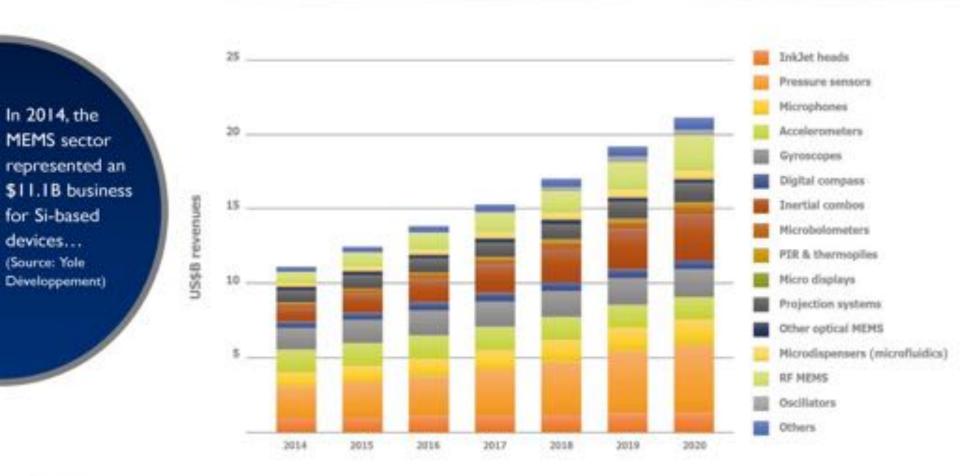

#### **MEMS Global Market**

#### MEMS MARKET FORECAST: 2014 - 2020 VALUE (IN B\$)

(Source: Status of the MEMS Industry, Yole Développement, May 2015)

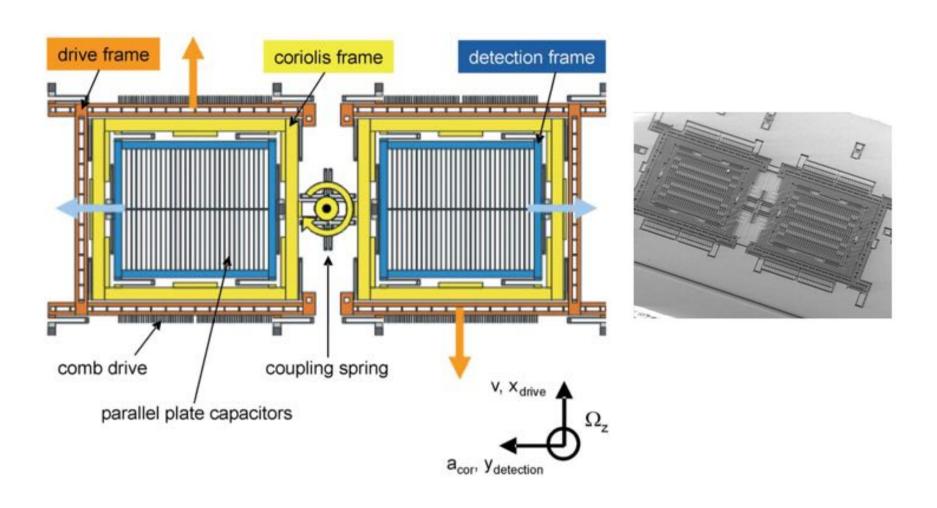

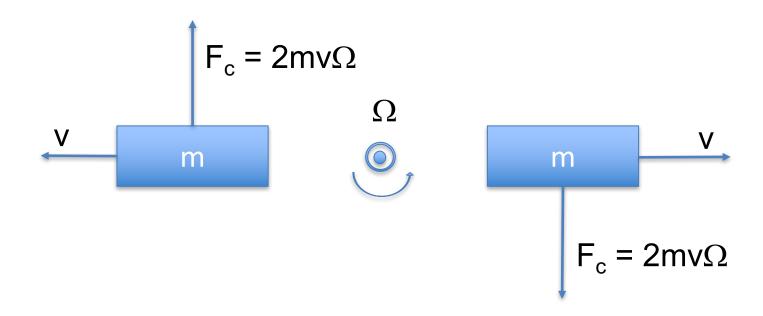

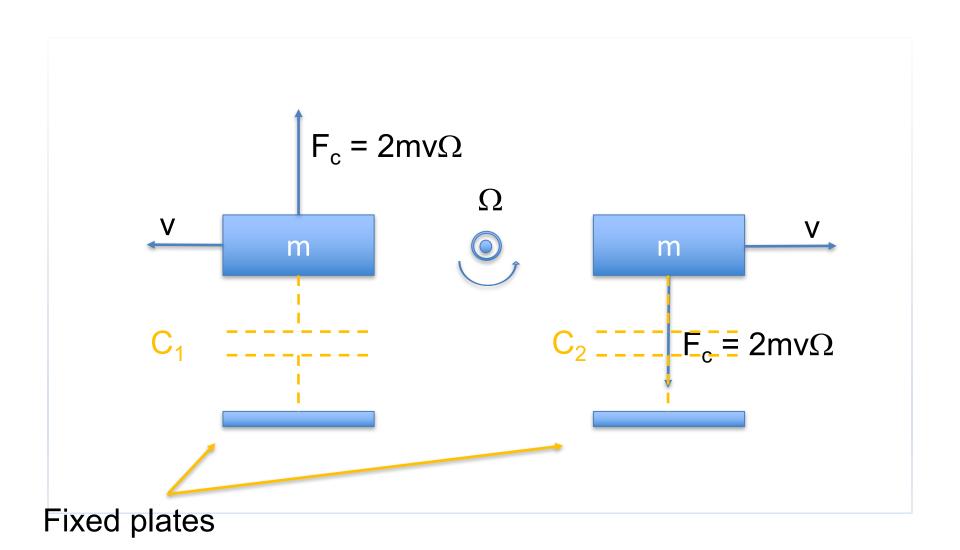

#### **MEMS** Gyroscopes

Traditionally used in navigation when the geomagnetic field is absent (i.e. in space) or disturbed (i.e. on a plane, in a tunnel).

#### NOW used in:

- Stabilization devices

- Robotics

- Tunnel Mining

- Weapons

When the GPS does not work (indoor, in space, in bad weather)

#### **MEMS Gyroscopes**

Traditionally used in navigation when the geomagnetic field is absent (i.e. in space) or disturbed (i.e. on a plane, in a tunnel).

#### NOW used in:

- Stabilization devices

- Robotics

- Tunnel Mining

- Weapons

When the GPS does not work (indoor, in space, in bad weather)

#### **Basic 1-axis accelerometer**

#### **Basic 1-axis accelerometer**

#### One axis accelerometer