All material: Chapter 2 of J. Rabaey, A. Chandrakasan, B. Nikolic, Digital Integrated Circuits, second edition, Prentice Halls, 2002

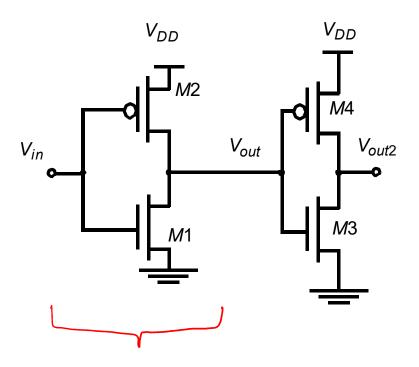

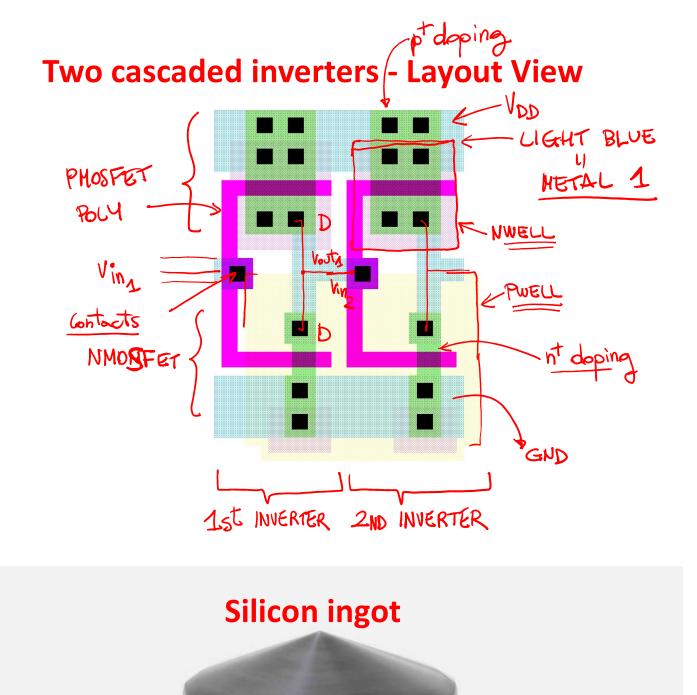

# **Two cascaded inverters**

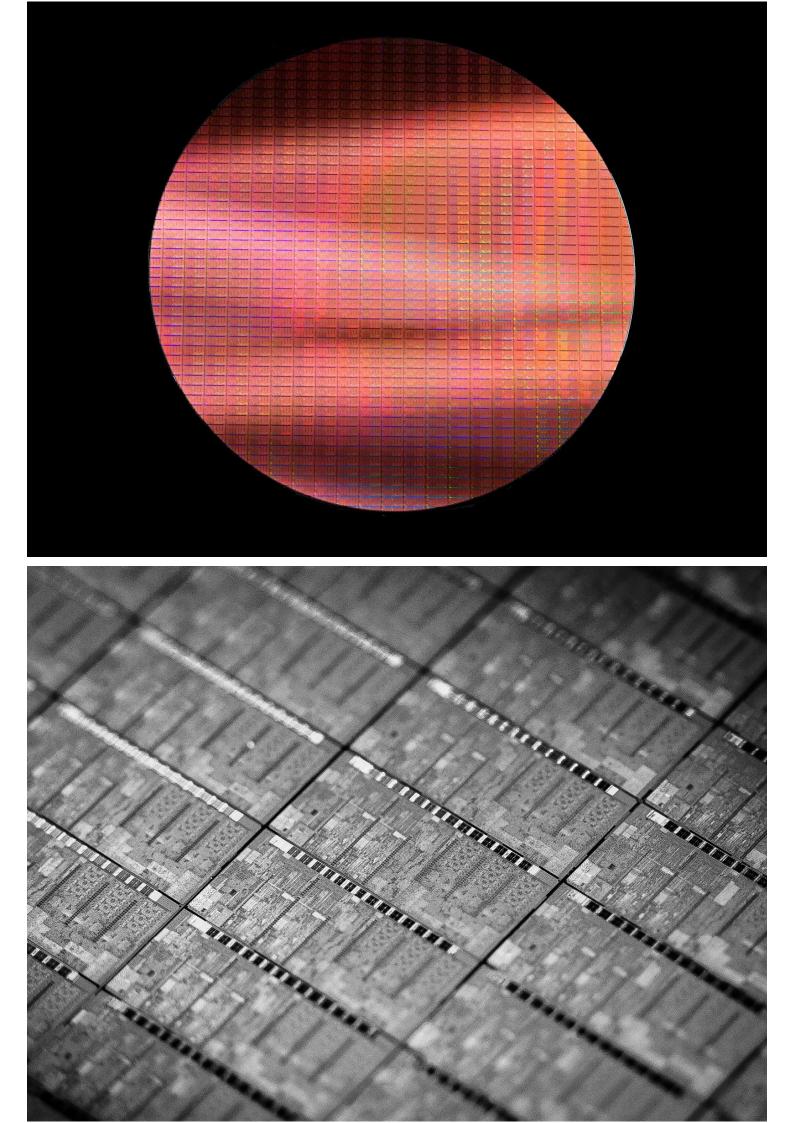

Water E< 1mm

Diameter 12 inches (300 mm)

5

Weight 100 Kg

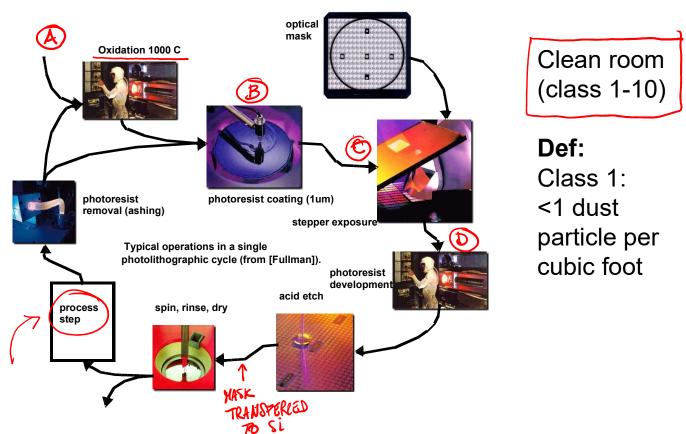

# **Photo-Lithographic Process**

In each processing step, an area of the chip is masked out using optical masks, so that the process step is selectively applied to the other regions

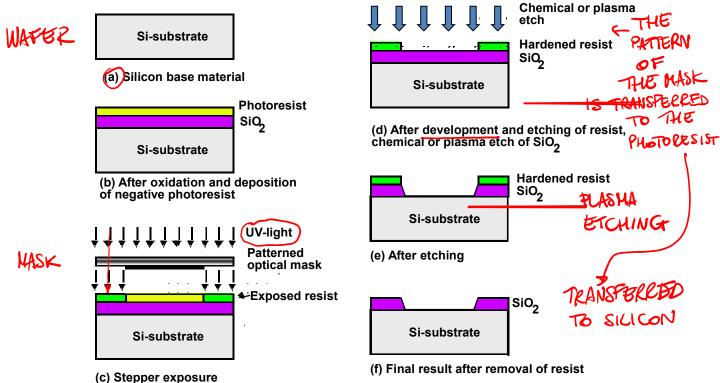

# Example of process step: Patterning of SiO2

# Recurring process steps (1/2)

- Doping

- Diffusion (gas with dopant, <u>900-1100</u> °C) –

- Ion implantation

- Lattice damage (displacement of atoms)

- →Annealing step (1000 °C for 15-30' + slow cooling)

- Deposition (of layers over the complete wafer)

- Oxidation [silicon oxide]

- Chemical Vapor Deposition: gas phase + heat (850 °C)\_ [silicon nitride]

- Chemical deposition (polysilicon: silane (SiH₄) gas over heated wafer (600 °C) → reaction an polysilicon formation Here

CHAMBER

Sputtering (for aluminum): evaporation in vacuum chamber

# **Recurring process steps (2/2)**

- Etching (defines 3D patterns on the surface)

- Wetetching (with acid or basic solutions)

- e.g. Hydrofluoric acid for silicon oxide

- Almost isotropic

- Dry or plasma etching

- Plasma: mix of nitrogen, chlorine, boron trichloride

- Strongly anisotropic (steep vertical edges)

- Planarization (flatten the surface to allow layer deposition)

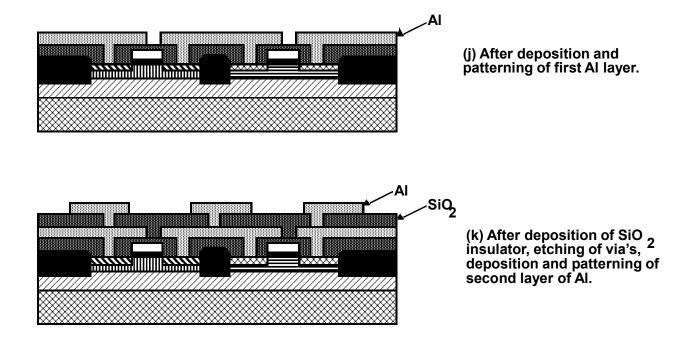

- Chemical Mechanical Polishing (CMP)

- Liquid carrier with a suspended abrasive component

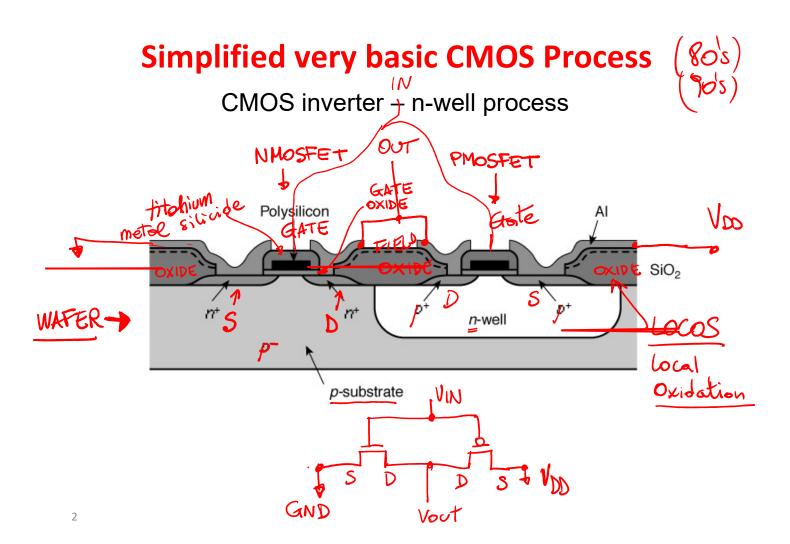

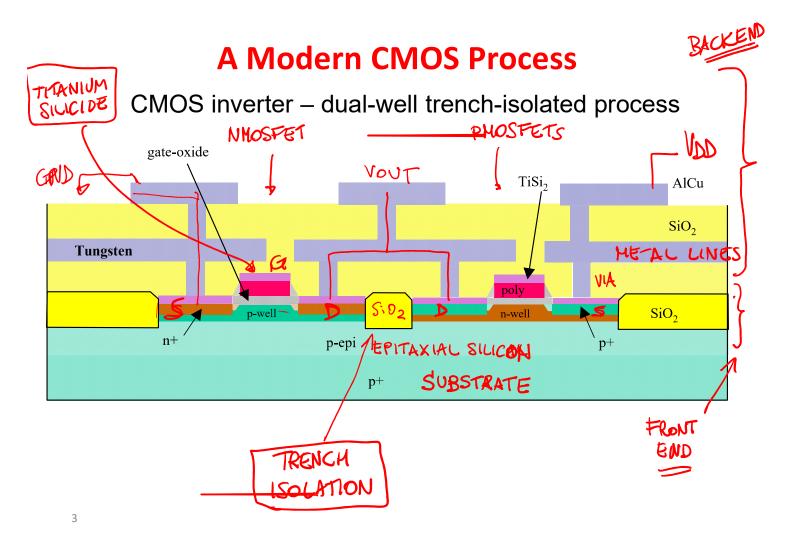

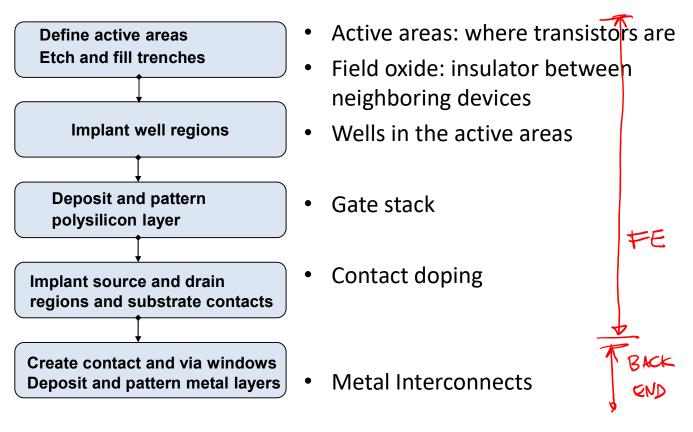

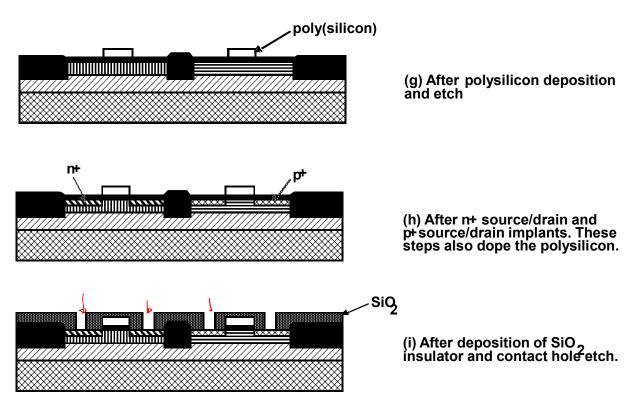

# **Simplified CMOS Process flow**

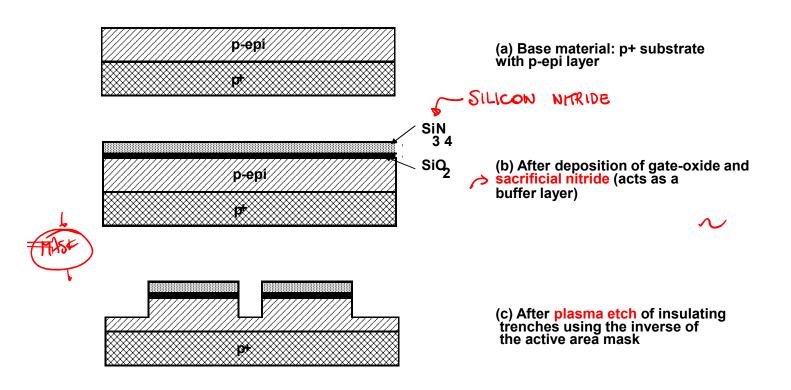

#### **CMOS Process Walk-Through**

13

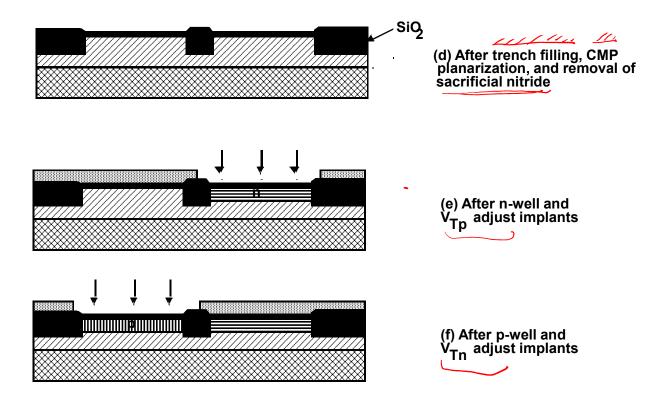

#### **CMOS Process Walk-Through**

#### **CMOS Process Walk-Through**

### **CMOS Process Walk-Through**

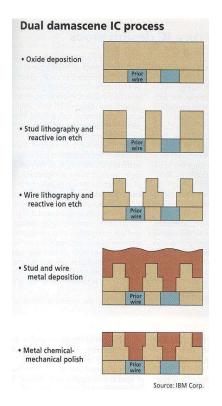

#### **Advanced Metallization**

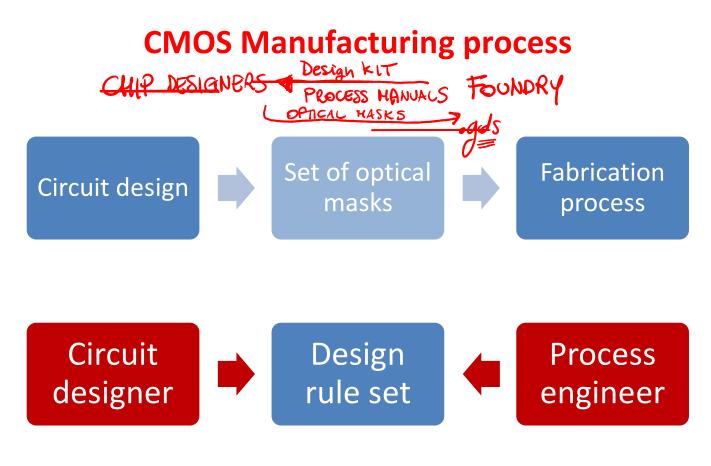

# **CMOS Manufacturing process**

All material: Chap. 2 of J. Rabaey, A. Chandrakasan, B. Nikolic, Digital Integrated Circuits, second edition, Prentice Halls, 2002

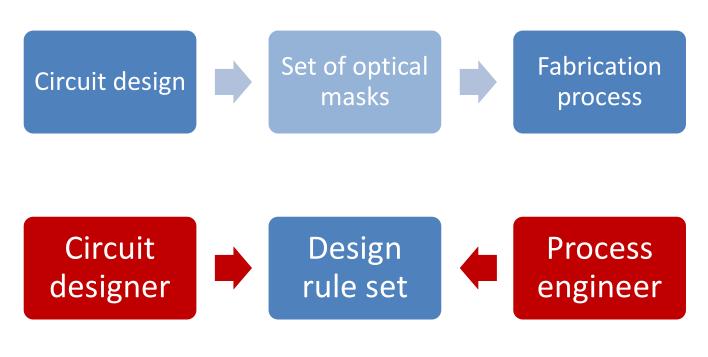

# **Design Rules**

- Minimum line width depends on lithography and process

- Micron rules: absolute dimensions for intra-layer and inter-layer layouts

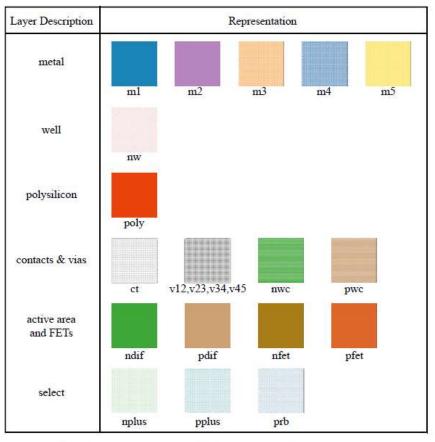

# Example: Layers in 0.25 $\mu$ m CMOS process

21

**Colorplate 1.** CMOS layers and representations (for vanilla 0.25 μm CMOS process)

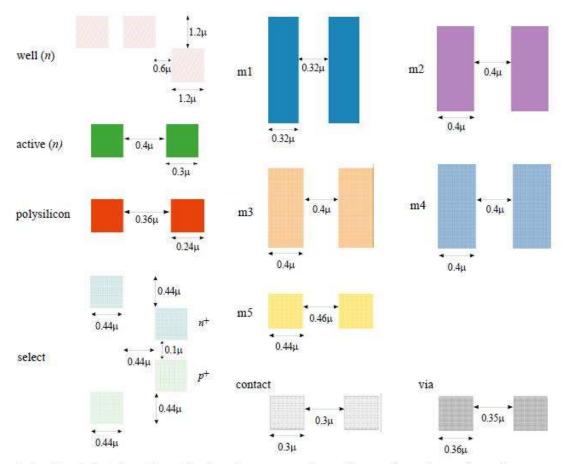

#### **Intra-Layer Design Rules**

Colorplate 2. Intra-layer layout design rules, expressed as minimum dimensions and spacings.

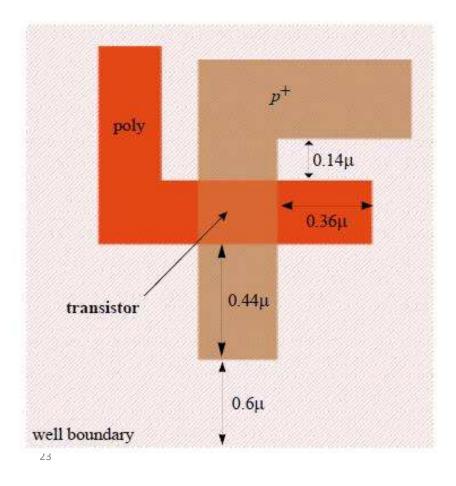

#### **Inter-layer rules: Transistor Layout**

**Colorplate 3.** Design rules concerning transistor layout. The device shown is a PMOS transistor.

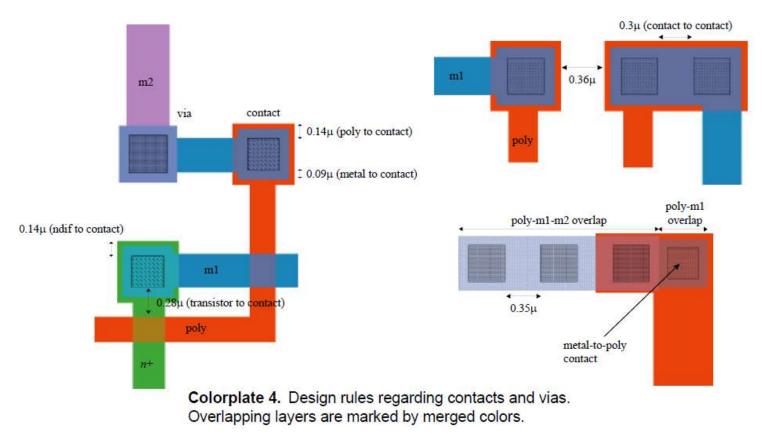

#### **Inter-layer rules: Vias and Contacts**

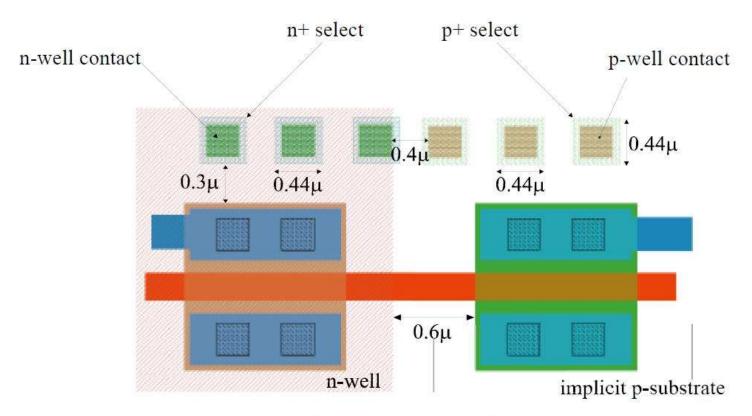

#### **Inter-layer rules: Select Layer**

**Colorplate 5.** Design rules regarding well contacts and select layers.

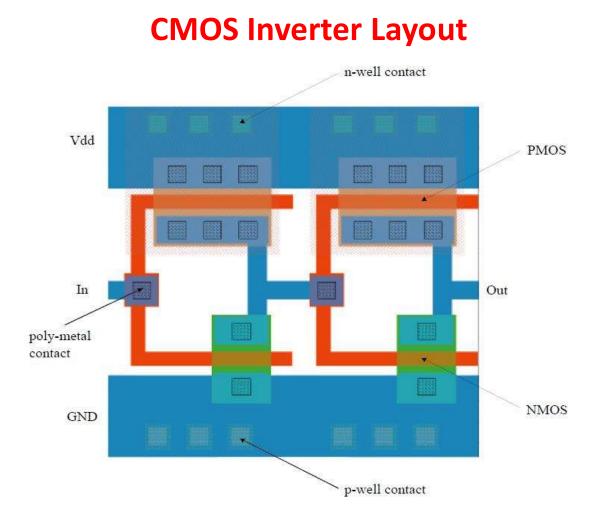

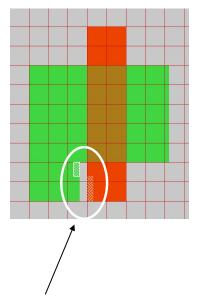

Colorplate 6. Layout of inverter in 0.25  $\mu$ m CMOS technology.

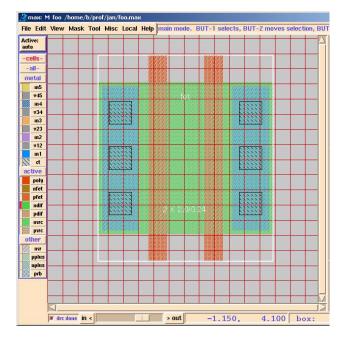

### Layout Editor & Design Rule Checker

poly\_not\_fet to all\_diff minimum spacing = 0.14 um.

27

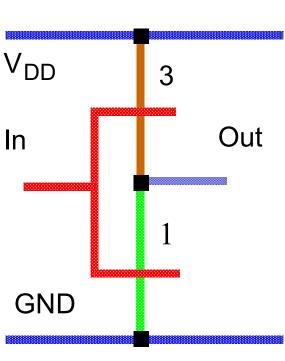

# Stick Diagram

**Dimensionless layout entities**

Only topology is important

Final layout generated by "compaction" program

#### Stick diagram of inverter

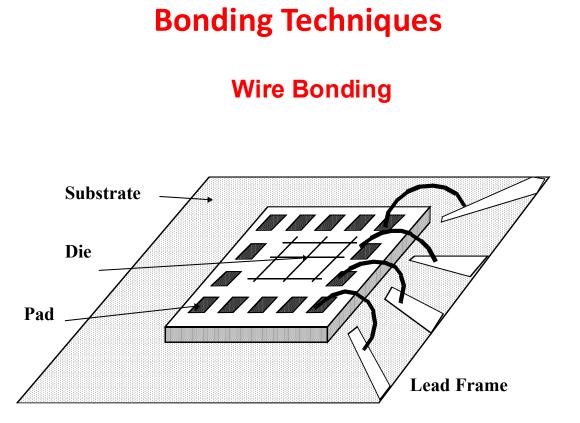

# **Packaging Requirements**

Packages must satisfy different types of requirements

- Electrical: Low parasitics

- Mechanical: Reliable and robust

- Thermal: Efficient heat removal

- Economical: Cheap

Gold wires, large inductance

29

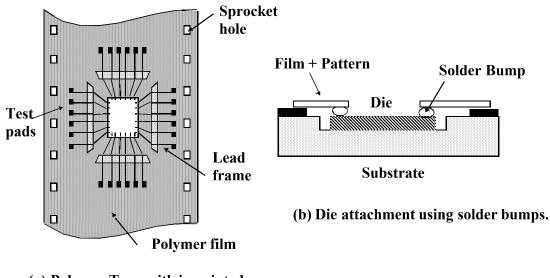

## **Tape-Automated Bonding (TAB)**

(a) Polymer Tape with imprinted wiring pattern.

31

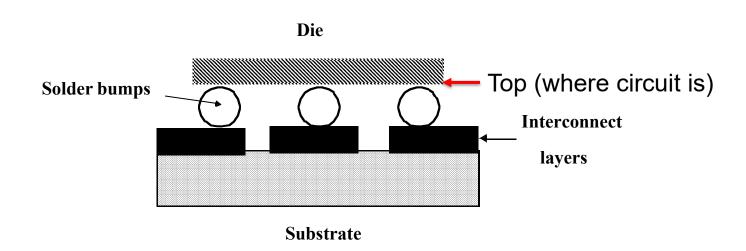

# **Flip-Chip Bonding**

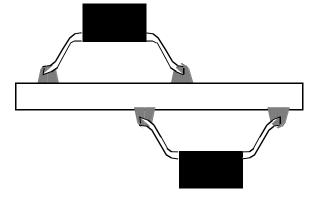

#### **Package-to-Board Interconnect**

(a) Through-Hole Mounting

33

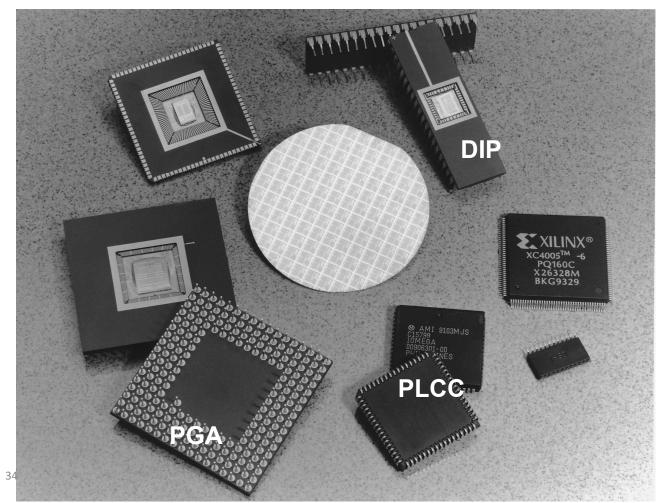

## Package Types

#### **Package Parameters**

| Package Type           | Capacitance<br>(pF) | Inductance<br>(nH) |

|------------------------|---------------------|--------------------|

| 68 Pin Plastic DIP     | 4                   | 35                 |

| 68 Pin Ceramic DIP     | 7                   | 20                 |

| 256 Pin Pin Grid Array | 5                   | 15                 |

| Wire Bond              | 1                   | 1                  |

| Solder Bump            | 0.5                 | 0.1                |

Typical Capacitances and Inductances of Various Package and Bonding Styles (from [Sze83])

35

## **Multi-Chip Modules**